verilog中if else和case语句有什么区别?

我认为if else当级数比较多的时候判断会比较慢,顺序一层一层往下判断,而case语句就不曾在这种问题,不知道我回答的对不对啊

串行和并行,以及优先级的问题

麻烦能不能说的稍微详细一点呢?

case和if-else都是串行执行的,唯一的不同是case是可综合的四态对比.if-else要么是二态对比,要么是不可综合的四态对比.

能详细解释一下吗?我觉得是一样的啊,都是含有优先级的判断,综合出来的电路也是一样的吧?好像如果在case语句那添加//synopsys parallel_case 就不一样了?

我认为是case语句做判断时是同时对所有的case情况同时做对比判断,是并行执行,而if else 是顺序执行先判断完if语句,在判断else语句。

if else和case语句都是有优先级的!case语句也是先判断写才前面的情况是否满足,前面的满足了就直接跳出case了吧。

都是串行的啊,都有优先级。

case应该是并行的

优先级不一样。

case在仿真的时候比if-else效率更高一点,另外,case语句在fpga的编译的时候更高效一点

case是并行的,而且case的每个判断条件是不能冲突的

不知道你是从哪看来的,你可以看一下verilog HDL综合 使用教程,孙海平译的2.14.5节,有明确指出。

你引用这些山寨教材有什么说服力,EDA先锋工作室的FPGA教材还说case是并行的呢。

Verilog 2001标准(IEEE 1364-2001)第132页:

- The case item expressions shall be evaluated and compared in the exact order in which they are given.

指出了case是串行有优先级。又:

- Apart from syntax, the case statement differs from the multiway if-else-if construct in two important ways:

- a) The conditional expressions in the if-else-if construct are more general than comparing one expression with several others, as in the case statement.

- b) The case statement provides a definitive result when there are x and z values in an expression.

a)是废话。b)指出了case是四态对比。除此之外和if-else没有差别。

又,根据ARM的“Verilog X Bugs”(http://www.arm.com/files/pdf/Verilog_X_Bugs.pdf) 第7页:

- Important things to note about case statements are listed below (which may help to dispel a few myths):

- · a Verilog case statement is priority encoded (just like a nested if expression)

- · the case-expression is effectively compared to the case-item with a triple -equal (===) case-equality

重复了以上说明。

这种1+1=2级别的东西是真心不想在这里啰嗦。标准不读,paper不看,只会道听途说,真是。

贝尔实验室的巴斯克写的书咋山寨了啊。比夏宇闻的权威多了吧。

Altera QuartusII中,使用parallel_case综合属性,可以让case语句综合成没有优先级的并行case逻辑。对于case, casex, casez都一样的。 语句需要这样写(注释部分很重要):

case (sel) // synthesis parallel_case

......

所以,一些资料中认为case是一定无优先级是不准确的。

以下是QuartusII 11.0 Help中“parallel_case”的关键字帮助的摘录:

--------------------------------------------------------------------------------

parallel_case Verilog HDL Synthesis Attribute

--------------------------------------------------------------------------------

A Verilog HDL synthesis attribute that directs Analysis & Synthesis to implement parallel logic rather than a priority scheme for all case item expressions in a Verilog Design File (.v) Case Statement.

......

其实要看具体环境,要是FPGA的话其实就是综合成查找表,if-else和case在有些情况下综合出来的电路时一样的。两者没有绝对优势,要看具体想怎么用。看RTL的话就是串行mux和并行MUX的区别,没有谁快谁慢的区别,如果两者跑的时钟是一样的话速度都是一样的。if-else有优先级,写在前面的条件的电路会靠近后级电路,这样优先将信号传入后级,前级即使满足条件也被后级给屏蔽了,建议可以写几个简单的case和else-if电路综合后看RTL图就能看出来区别了。

引经据典一大通,不如用Synplify 2013来试试综合结果吧。

相信理解不了if-else和case区别的人(不考虑验证,就是完全没有区别),抓破脑袋都看不懂这个综合结果。

(1)用if-else写一个并行MUX

- module parallel_if(input a,b,c,input [2:0] sel,output reg y);

- always@(*)

- if(sel==3'b001)

- y=a;

- else if(sel==3'b010)

- y=b;

- else if(sel==3'b100)

- y=c;

- else

- y=1'bx;

- endmodule

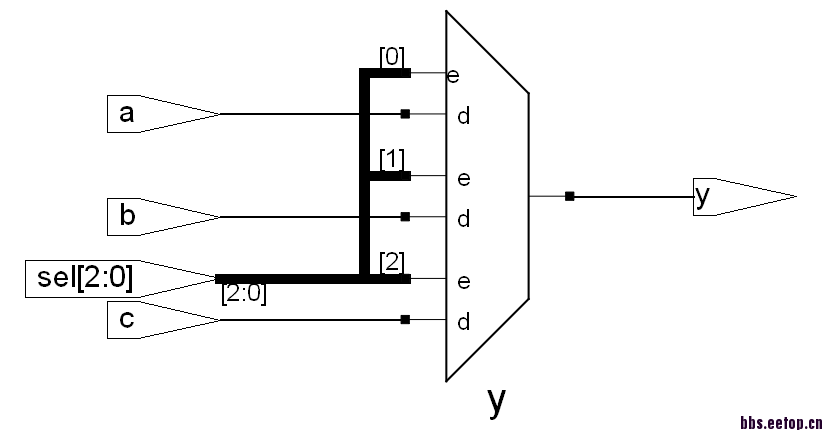

RTL图,怎么样,用if-else也可以写出并行MUX吧?

(2)用case写一个串行MUX

- module serial_case(input a,b,c,input [2:0] sel,output reg y);

- always@(*)

- case(1'b1)

- sel[0]:y=a;

- sel[1]:y=b;

- sel[2]:y=c;

- default:y=1'bx;

- endcase

- endmodule

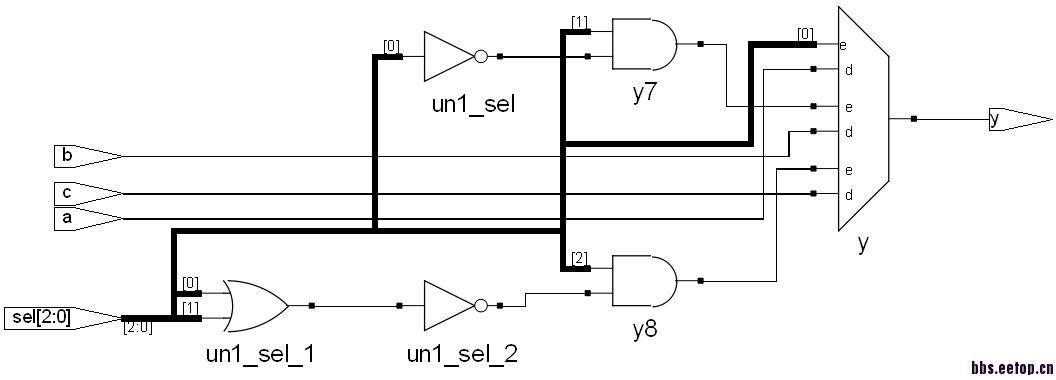

RTL图,怎么样,用case也可以写出串行MUX吧?

PS:添加parallel_case属性就可以综合成第一个图的结果,见证奇迹的时刻喔

不信的,请自行用Synplify 2013试验。(用Precision Synthesis也可以,但用Quartus/XST可能看不到上面的结果,因为这两个例子对综合工具的Elaborate能力要求较高。是不是也应该把这个例子加入QoR Benchmark)

具体还是和代码怎么写的有关系,如果是one_hot的编码方式,会综合成并行电路,就前面的if_else

例子一样。

犀利,小白学习了!

这样两个综合出来的结果不一样。 可以去看看Synopsys 的Design Complier manual

结合自己的应用,特意查了下资料,if-else语句可以实现有优先级的电路,而case语句,一个case分项的分支表达式的值必须互不相同,否则就会出现矛盾现象(对表达式的同一个值,有多种执行方案)。对于那些分支表达式中存在不定值x和高阻值z时,case语句提供了处理这种情况的手段。下面的两个例子介绍了处理x, z值case语句

带优先级if else的路径长一些,case是并行结构,路径短,速度快。不过4选1的综合工具会优化,差别应该不大,可以试试16选1的。

学习了

学习了

学习了。

我也觉得if-else带有优先级,路径会长些……case没得优先级,路径会短些……

当条件少时用ifelse,条件都时用case,综合出来效果不一样。

case 是并行执行。