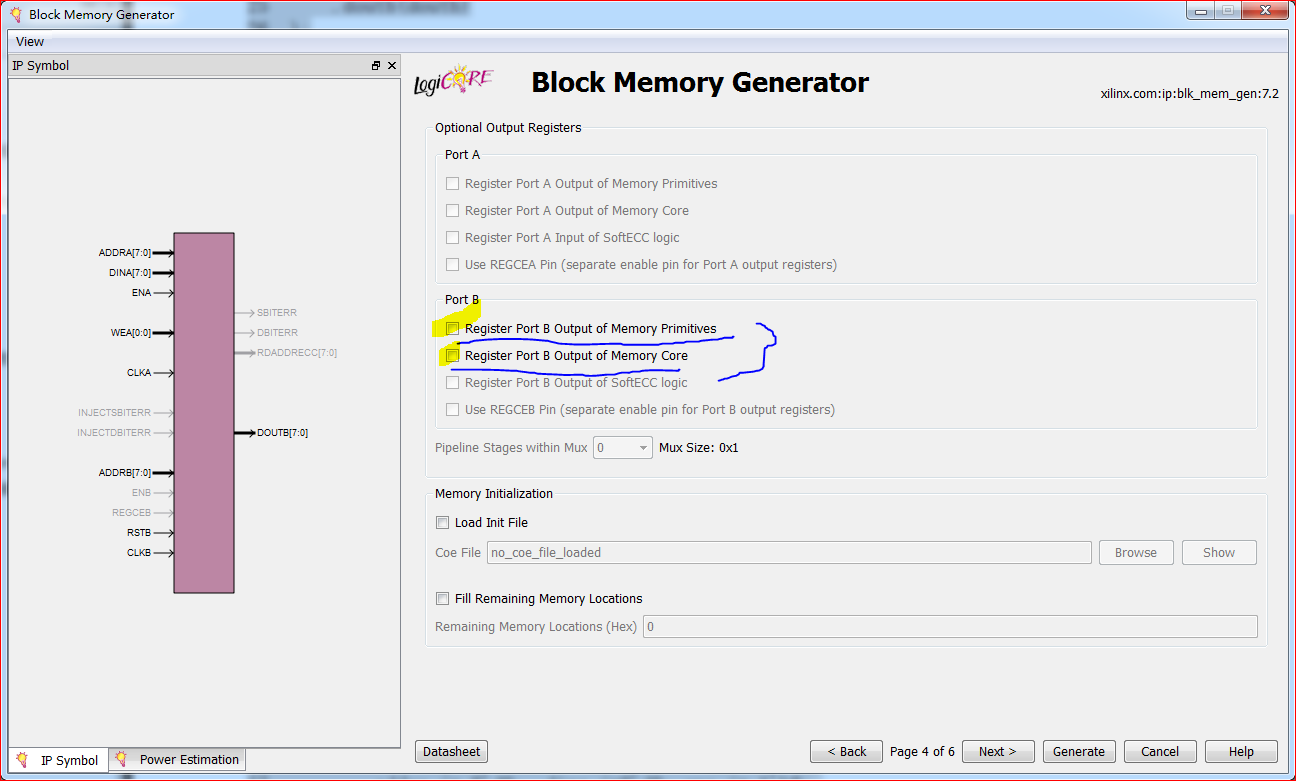

简单双口RAM输出寄存器选择

时间:10-02

整理:3721RD

点击:

想知道这个选项该怎么设置?我看有些资料上写:寄存器输出方式可以提高性能,改善时钟延时,如果选择寄存器输出需要增加相应的时钟周期来输出数据。

然而我参考有些设置的RAM核的例子,这两个选项都没有选择,但是输出波形与选择其中任意一个的时候输出的波形都一样。也就是说,在某些情况下,选择与否对输出波形没有影响。

我也有参考IP—datasheet,并没有看出这两个选项的意思,希望大神们可以给指点下;谢谢!

勾上这个选项,数据输出会在原来的基础上多一个时钟的延迟,我一般不勾这个选项,数据输出一个时钟周期的延迟。

那你是选择寄存器输出还是核输出?延时输出是相当于读地址信号吗?还是读时钟周期?

在低速操作时应该没有任何区别,使用block ram内部的寄存器应该是可以提高速度以及节省外部FF。不过对于我自己,一直都是没有用过它的。

ram的clk_to_q的延时是很高的,在clk频率很高的应用下,如果ram q端输出直接接到外面的组合逻辑很可能会出现setup violation,这个时候就可以在q端加一级寄存器输出改善时序,低速应用无视他就好了

相对于地址信号

恩,是的,测了几种情况的波形,确实没有什么区别

恩,我现在设置的时钟是低速的,谢谢你,