请问大神们,如何验证DDR3与FPGA是否正确连线?

求解求解

在example design中有一个par的文件夹,里面有一个creat_ise.bat的批处理文件,运行这个批处理文件,就会在par文件中建立一个ise的工程。

打开建立好的ise工程,可以看到顶层文件是example_top.v。

这个工程是专门用来测试ddr3的,如果你想要测试连通性,需要再example_top.v中Cx_px_DATA_MODE改为4‘b0101或者4'b0110,即使用walking0或者walking1的方式测试。

详细的说明可以看看UG416 "MIG Example Design with Traffic Generator"的章节

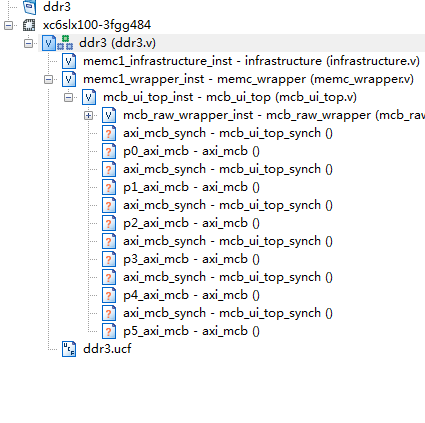

首先谢谢你啦~ 这是我运行create_ise.bat后的所有文件列表,发现里面没有ISE的工程文件,不知道这是什么原因?还有,双击create_ise.bat后 cmd窗口一闪而过,不知道算不算运行成功?

1.打开命令行

2.cd到bat的目录

3.在命令行下运行 bat

4.看看是什么原因造成的bat运行失败

5.很有可能是你没有ise的路径添加到环境变量当中

找到了 运行后的ISE工程文件生成在了上上一级文件夹下 嘿嘿 多谢多谢~

你最好上美光的网站下载一个模型,然后测验证一下。那个靠谱点。

ddr3,初始化的init_calib_complete信号仿真能拉高,下到板子上就一直为低,请问可能是啥问题。或者给个联系方式指导下

ddr3,初始化的init_calib_complete信号仿真能拉高,下到板子上就一直为低,请问可能是啥问题。或者给个联系方式指导下

ddr3 挺高端的

?

你好,我现在也遇到这个问题请问你当时是怎么解决的,谢谢!如何验证DDR3与FPGA是否正确连线?