关于LPDDR2 SDRAM读写数据的问题

时间:10-02

整理:3721RD

点击:

我现在使用的是xilinx的lpddr控制器ip,lpddr大小512Mb。写数据正常,且在dq数据线上能看见该有的数据,但是读数据的话,给了相应的地址后,读数据在读出512个数据后就始终为零,而此时dq呈现不定态。所以很困惑,请各位大侠帮忙解决问题。

写正常不正常看数据线不能充分证明。

读正常才能说明写正常。

看看读是不是正常?

写正常吗?

ip core配置细节。

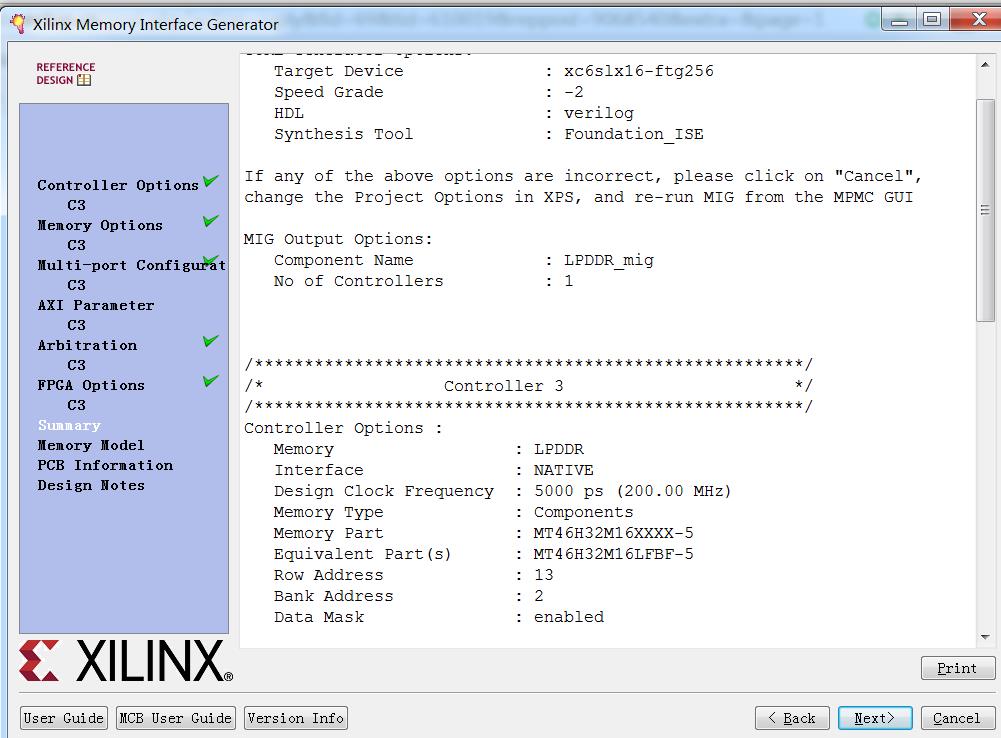

在数据量小于512个数据时读和写都是正常的,从读数据通道看,写入什么读出的是什么,顺序什么的也对,也不丢数据。第513个数时读数据rd_data突然变成零,此时dq通道变成之前未出现过的不定态,这时候写还是之前的情况,看不出异常。下图是我的ip配置,不知是不是配置有误,求教,谢谢~

并没有看出什么问题。

极有可能就写进去这么多数,超过512的就没写进去

从mig本身的数据通道上看,在写状态下是有大于512的数据量出现的。但是如果说真没有写进去的话,是什么原因造成的呢?可以有什么办法像之前那样写进去数据呢?

写接口是什么,axi,ahb?

512个数据是否刚好一页?

写接口不是带axi型的,就是普通接口。512个数我算了一下,刚好是一个bank的一行,它是bank-row-colunm的地址寻址方式,所以感觉是在跳往下一个bank的时候出问题的。但是如果改变首地址,也能存,能跳到下一个bank,只是最后会丢几个数,很奇怪。所以请教这会是什么问题呢?

看看bank row col的地址是否有超出512MB