使用MIG工具生成的DDR驱动在MAP阶段报错

时间:10-02

整理:3721RD

点击:

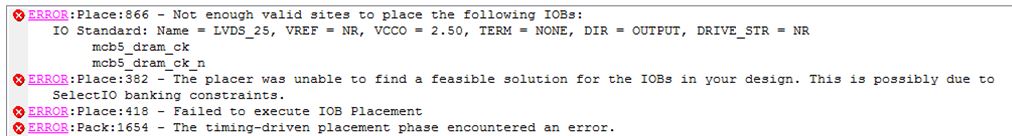

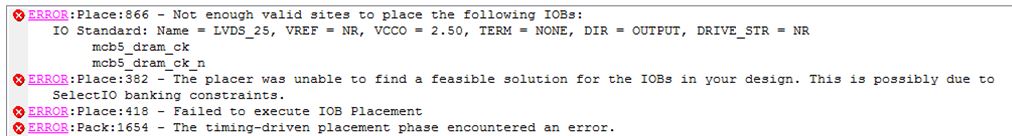

最近由于工作需要,开始接触赛灵思公司的MIG工具,生成了一个简单的MCB核,我在MIG工具里将MCB配置成两个单向(一个读一个写)32bits位宽端口,MCB系统时钟、命令时钟和读写时钟都用一个时钟,translate阶段报错后修改了MIG工具生成的一个文件,把里面的用到ibufg的部分给注释掉了,然后translate通过了,但是在map阶段却报出下图的错误:

ucf文件没有改,芯片是spartan6系列的。

ucf文件没有改,芯片是spartan6系列的。

不~~要~~沉~~啊~~啊~~~

没有人遇到过类似的问题吗?给个建议吧~~大神们啊~~~

应该是你的bank电压和IOSTANDARD不匹配,该bank的其他的IO标准为1.5V或1.8V,而这个LVDS是LVDS_25

没有足够的LVDS_25属性的管脚。和硬件工程师沟通一下。