有关Altera PLL重配置输出频率问题

故需要自己来写的模块去实时改变各counter_type下counter_param的值来实现想要输出频率的调整。

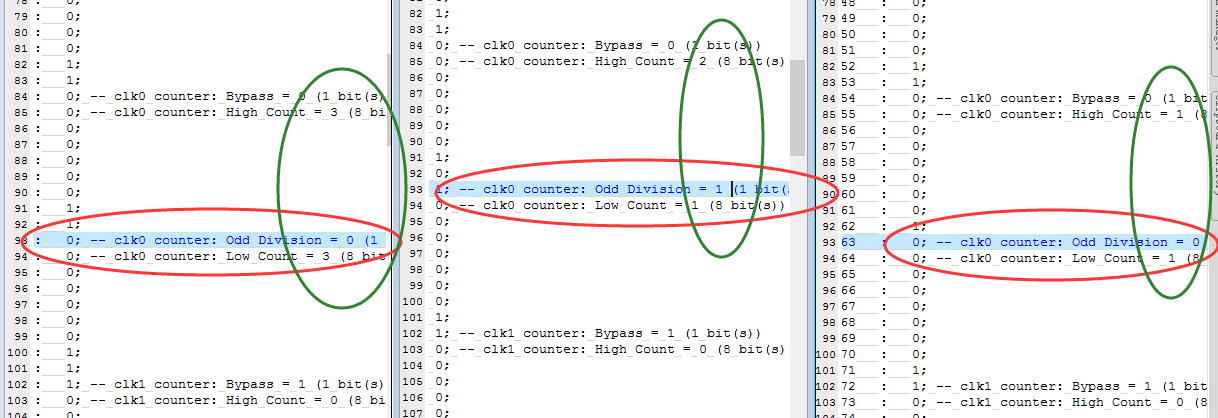

若只是改变频率保持相位不变及带宽自动调整,观察了pll产生的对应各个频率的mif文件内容,

基本上不同频率主要只涉及到如下参数变化:

N counter: Bypass、Odd Division、High/Low Count

M counter: Bypass、Odd Division、High/Low Count

clkn counter: Bypass、Odd Division、High/Low Count

从网上搜的资料讲到Odd Division只与相位有关,但发现Odd Division=1或0时对输出频率有明显影响。

在官网的pll及pll reconfig相关handbook上也未找到有关Odd Division的具体解释。

请问当Odd Division=1时,pll输出频率如何计算,公式是什么?

非常感谢!

自己顶一个,不能沉了!

帮帮忙啊!

建议小编还是生成mif重配,一般这种PLL参数官方是没有release出来的,可以问问FAE。不同器件的PLL的VCO都是有一定的频率范围的,如果你贸然的动态修改某个参数的值,非常有可能造成配置参数超过VCO频限

谢谢你的回复,实在不行就只能弄很多个mif文件做选择了。

这两天刚好研究了PLL重配置,关注到了你这个帖子,仔细研读了相关文档之后,通过Quartus软件生成了几个mif文件,打开研究了里面的数据,其实Odd Division=1或0对输出频率没有影响,只是影响了占空比,你如果是看到影响很大,可能是因为你没有仔细看前后的数据。[attach]663104[/attach],这是我打开的几份mif文件,分别为100、200、300M,你对比下。odd divsion确实有时候不同,输出的clk差的也很大,但是由于count的高低位决定的,它有时为1(如果 占空比默认为50%),则是因为count需要为奇数才能得到我们想要的频率,此时为1就可以保证输出50%的占空比。具体的公式为Fout = Fin(M/(N*C)),仔细研究下相关文档就可以了。

具体文档可参考《Implementing PLL Reconfiguration in Cyclone III Devices》

《Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction》

《Implementing Fractional PLL Reconfiguration with Altera PLL and Altera PLL Reconfig IP Cores》