同步FIFO时序仿真与功能仿真不一致

时间:10-02

整理:3721RD

点击:

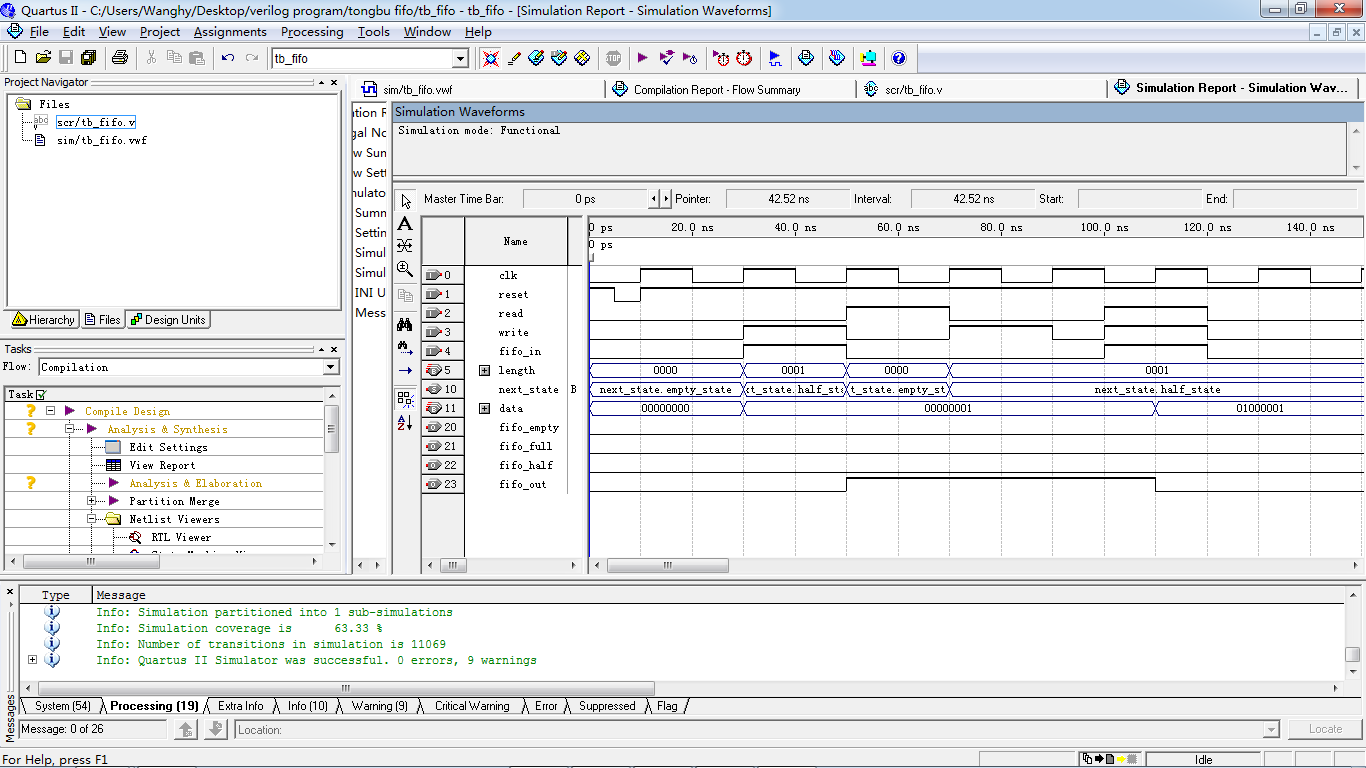

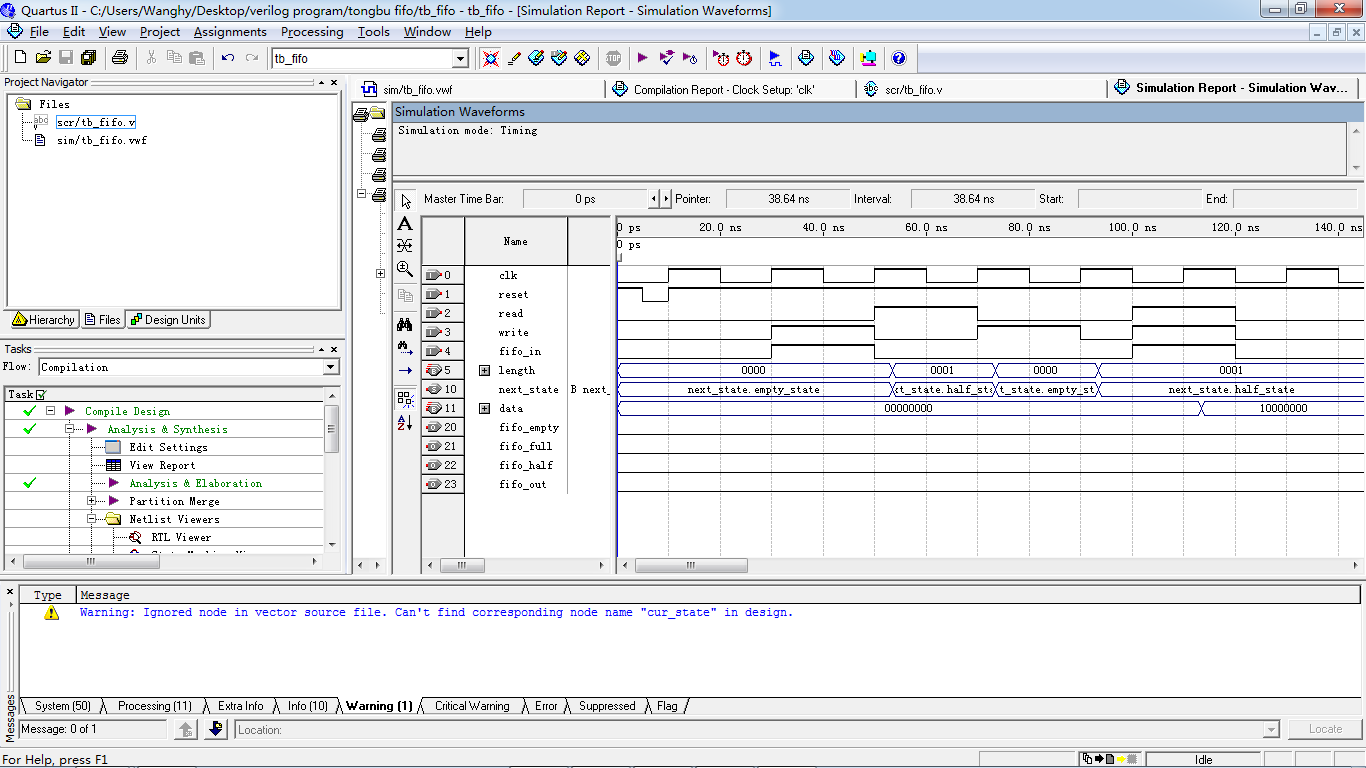

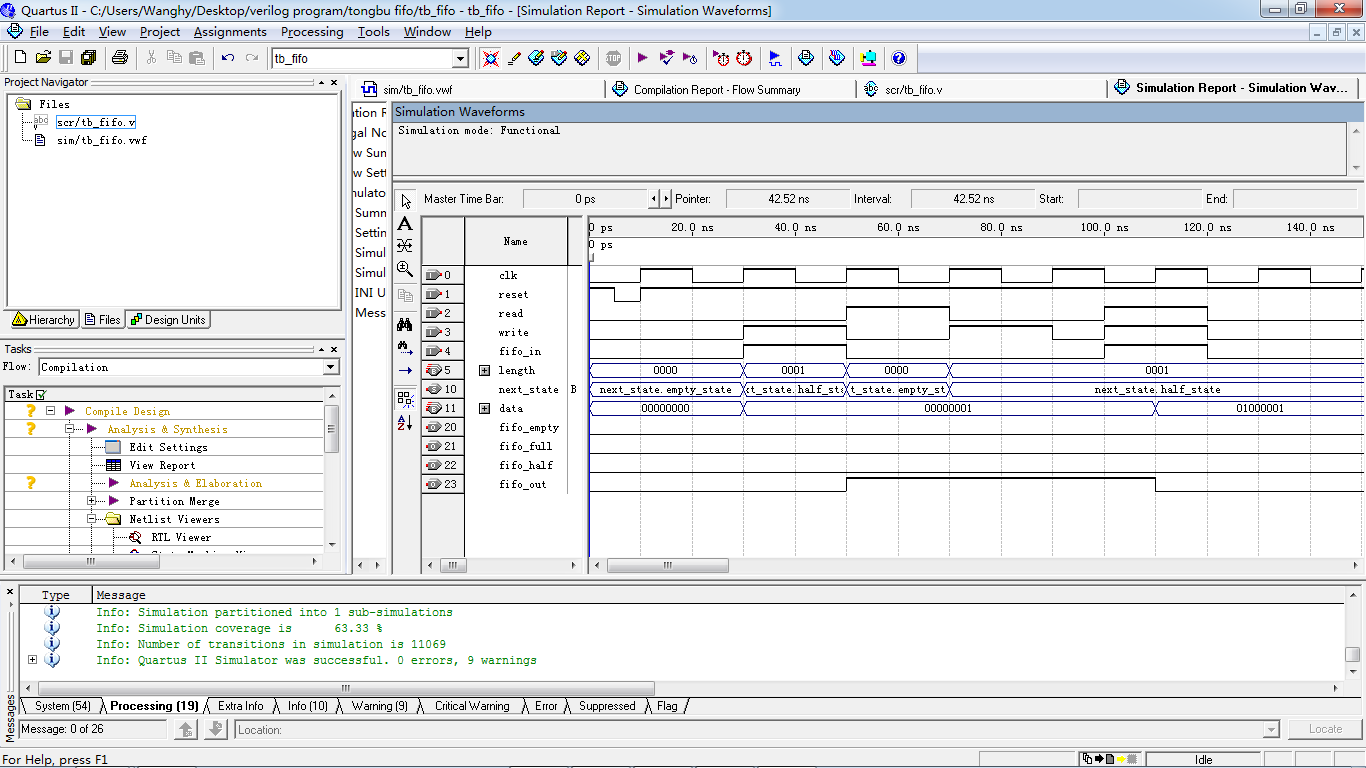

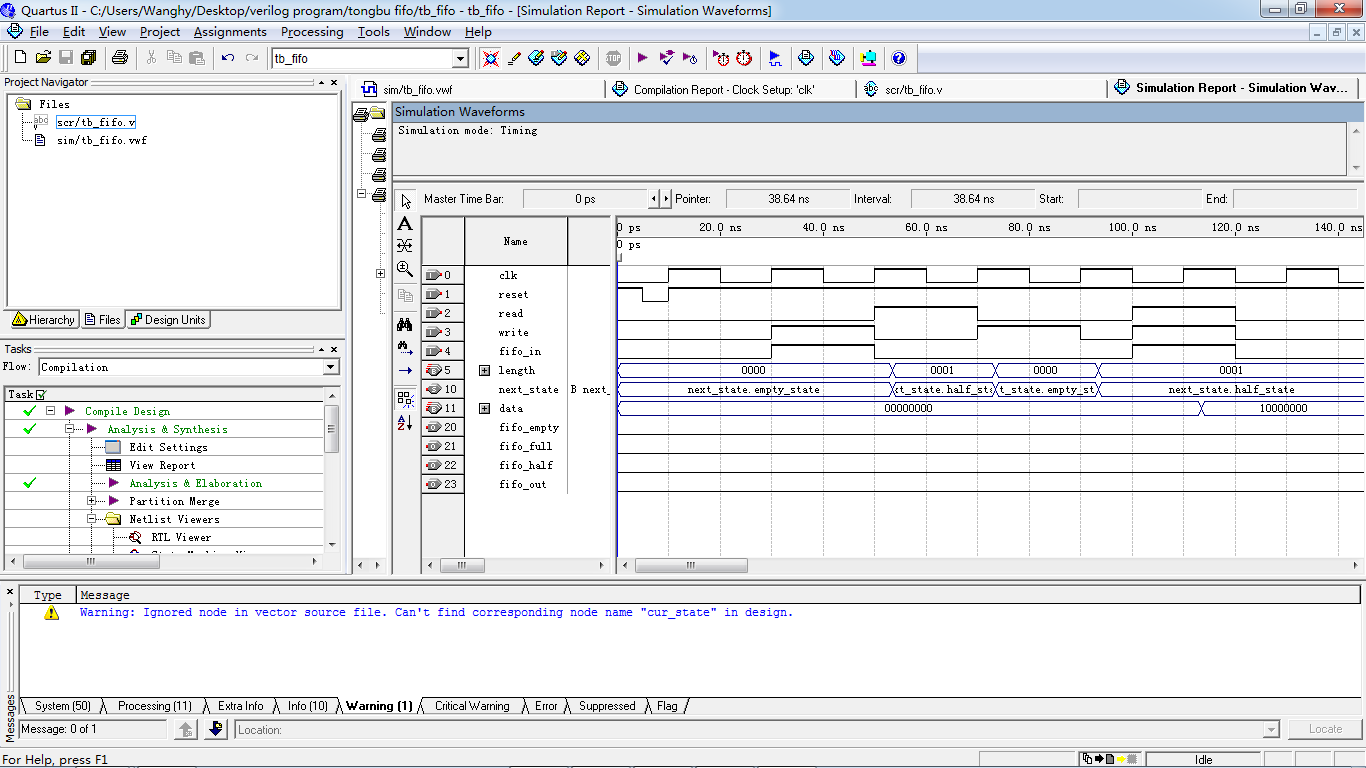

写了个同步FIFO的程序,结果功能仿真与时序仿真的结果不一致,可是时序分析的结果没有看出时序仿真表现出来的那么大的延迟,这是为什么?这个延迟怎么来的?一般碰到这种情况应该从哪方面入手?谢谢!以下分别是:功能仿真、时序仿真、时序分析图(fifo_empty、fifo_half、fifo_full我没有输出,不用管,主要是length:队列长度、nextstate、data:队列数据这三个有问题)

把read、write、fifo_in等输入信号在testbench中用clk的下降沿触发,估计你现在是用的上升沿触发,时序仿真肯定会出问题的。

我知道了,我也知道原因是什么了。谢谢!