FPGA-VIP视频工程开发连载1——DDR2控制器

时间:10-02

整理:3721RD

点击:

FPGA-VIP视频工程开发连载1——DDR2控制器

工程实例下载地址:http://pan.baidu.com/s/1hqJx3tMhttp://pan.baidu.com/s/1hqJx3tM

http://pan.baidu.com/s/1hqJx3tM

功能简介

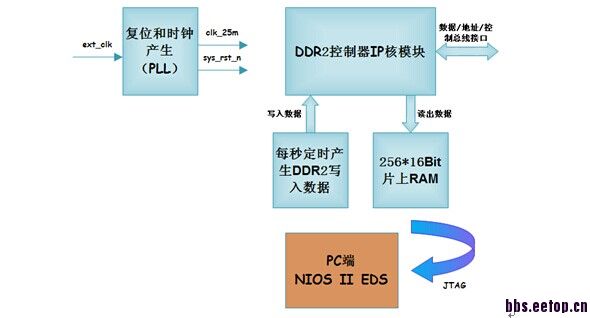

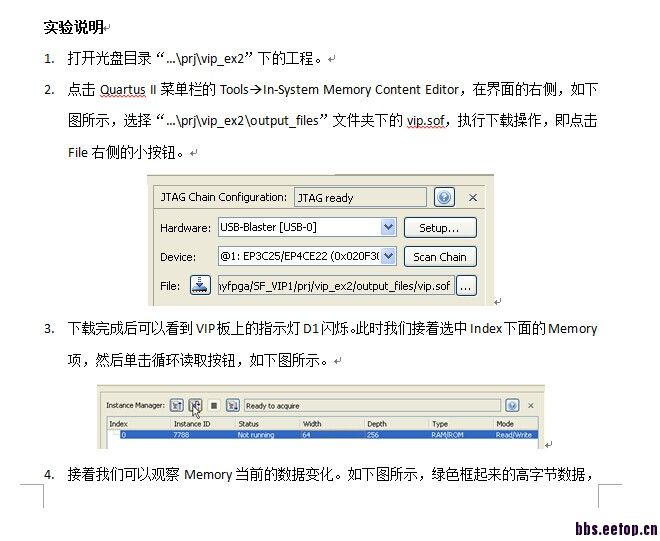

本实例对Altera提供的DDR2控制器IP核模块进行操作,每1.78秒执行一次DDR2的写入和读出操作。先是从0地址开始遍历写256*64bits数据到DDR2的地址0-1023中;在执行完写入后,执行一次相同地址的读操作,将读出的256*64bits数据写入到片内RAM中供查看。在In-System Memory Content Editor中可以查看有规律变化的数据。

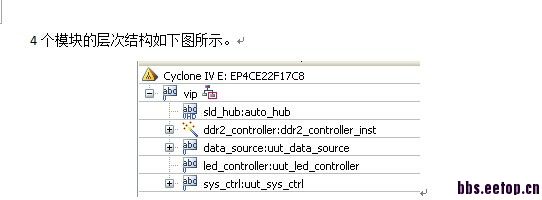

本实例有4个模块。

●

Vip.v是顶层模块,其下例化了3个模块。

●

Sys_ctrl.v模块中例化了PLL,并且对输入PLL的复位信号以及PLL锁定后的复位信号进行“异步复位,同步释放”的处理,确保系统的复位信号稳定可靠。

●

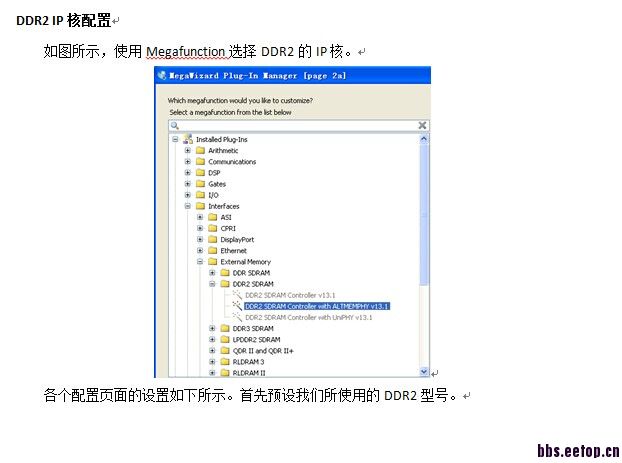

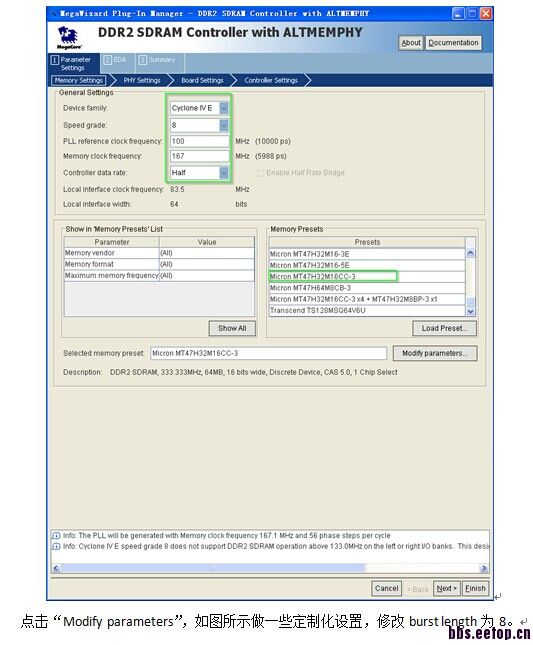

Ddr2_controller.v模块是使用Mefunction例化的DDR2控制器IP核模块,这个模块预留了DDR2的读写控制接口供FPGA逻辑侧进行操作。

●

data_source.v模块主要用于和DDR2控制器进行数据交互,它既产生写入DDR2的数据流,也读出DDR2已经写入地址的数据,同时将这些数据送往例化的onchip RAM中。

学习了。

学习学习。

学习学习学习。

感谢小编,学习了

我太需要這篇了~感謝!