请问这样子赋值为什么会使后面的case语句出现错误?

时间:10-02

整理:3721RD

点击:

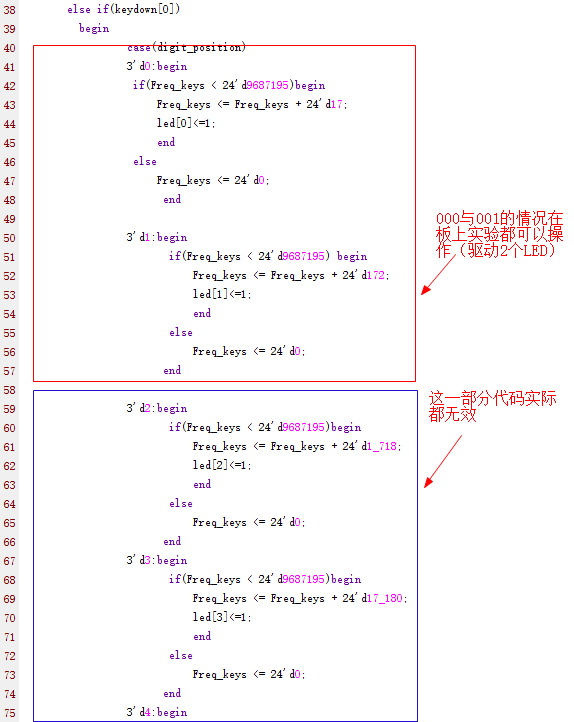

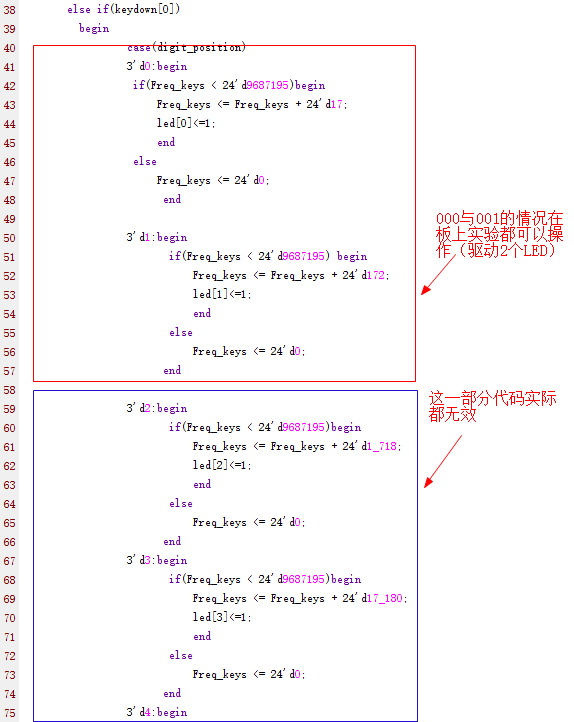

我希望通过按键切换控制的数字位

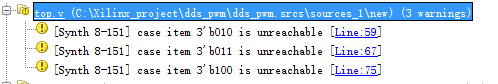

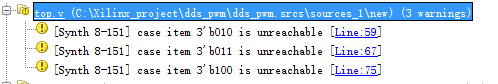

这是message的warning

- reg digit_position;initial digit_position=3'd0;

- always@(posedge clk)

- begin

- if((keydown[1])||(digit_position>4))

- digit_position<=3'd0;

-

- else if((keydown[3])&&(digit_position<5))

- digit_position<=digit_position+3'd1;

-

- else if((keydown[4])&&(digit_position>1))

- digit_position<=digit_position-3'd1;

- end

这是message的warning

所以FPGA上只会工作led[0]和led[1],led[2]、led[3]、led[4]都没有工作

因为你的digit_position只有1bit,只有0和1两个分支,其它都是unreachable.

+1!

语句:reg digit_position;表明你所定义的寄存器类型为1位宽,因此你的digit_position只会是1'b0或1'b1,当然不会跳到后续状态上去。应修改为reg [2:0] digit_position;

谢谢大家,我已经解决了,正是因为位宽不匹配问题!

华科学长好啊,求私聊QQ393756200