verilog case语句遇到的问题

时间:10-02

整理:3721RD

点击:

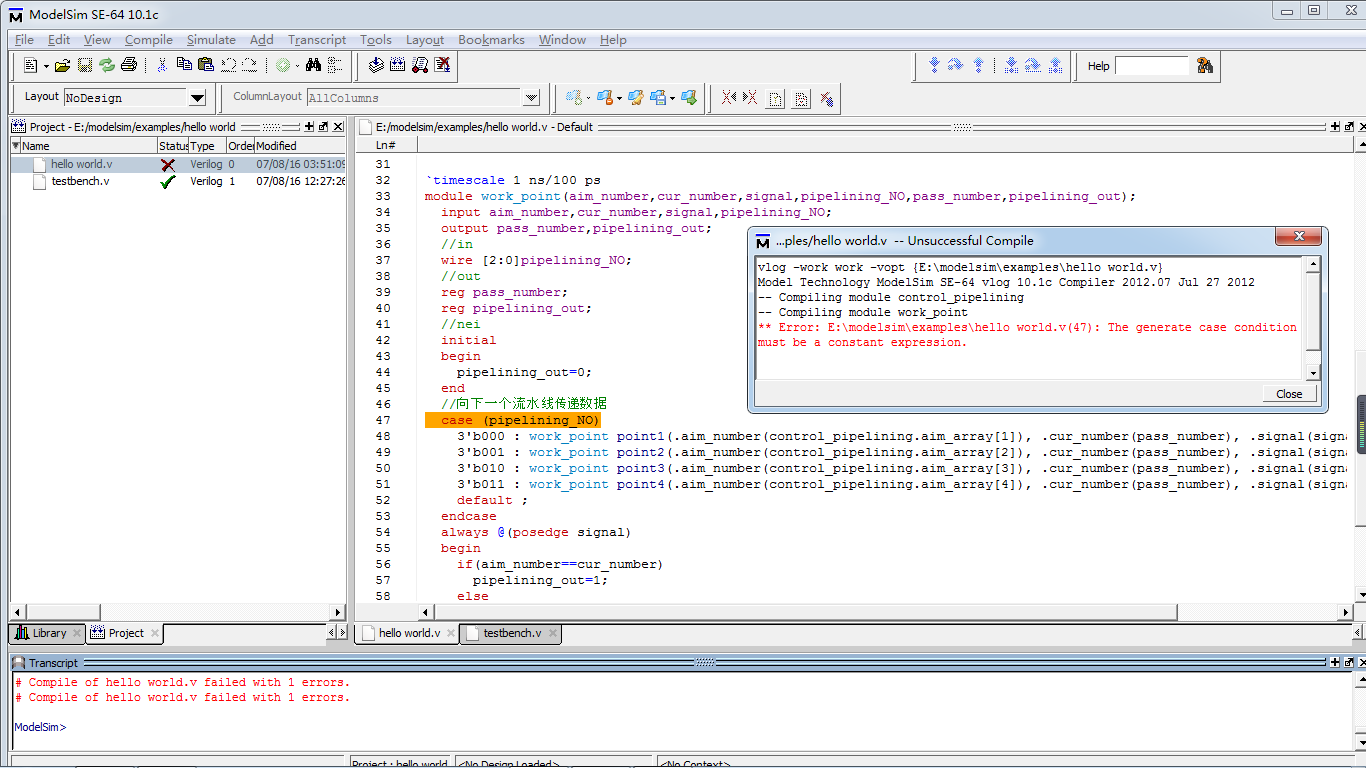

这个case语句哪里有问题?生成条件必须是常量表达式?什么意思?是用来判断的那个条件用的有问题吗?谢谢!

这个case语句哪里有问题?生成条件必须是常量表达式?什么意思?是用来判断的那个条件用的有问题吗?谢谢!

平时用的判断条件都是寄存器型的变量

你要是分不同情况去例化模块,要用case generate 语句,并且case里面不能是变量,必须是常量参数

看你的代码,其实你可以直接把这四个模块都例化在那里,然后根据pipelining_no信号去做个mux,选择这四个模块其中一个输出给output就好

楼上说的对,

谢谢,我知道问题在哪了。可是关于case语句还有个问题,如果case后面必须是常量参数,那怎么用case实现根据不同情况选择不同操作?常量参数不是=确定情况吗?

你可以根据需要在不同的地方例化的时候,传递不同的参数,比如例化两个a模块,第一个传递参数01,第二个传递10,这样会自动生成不动的

看你目前这一小段代码,你直接把四个都例化了

然后输出做个mux

output_signal = pipileline_no == 0 ? a_out :

pipileline_no == 1 ? b_out... 就好了

好的,谢谢了!

怎么小编的代码看下来是在递归啊。

是,不过现在不用了

小编你当这是C程序啊

我就是原先学的C,现在刚开始学的verilog。

放到always里面去

要写成标准的CASE生成语句模式,你那写法是错的,详细百度生成块的写法。

case语句要么放在initial里,要么放在always里

直接放在module里当然报错