逻辑分析仪求教,

时间:10-02

整理:3721RD

点击:

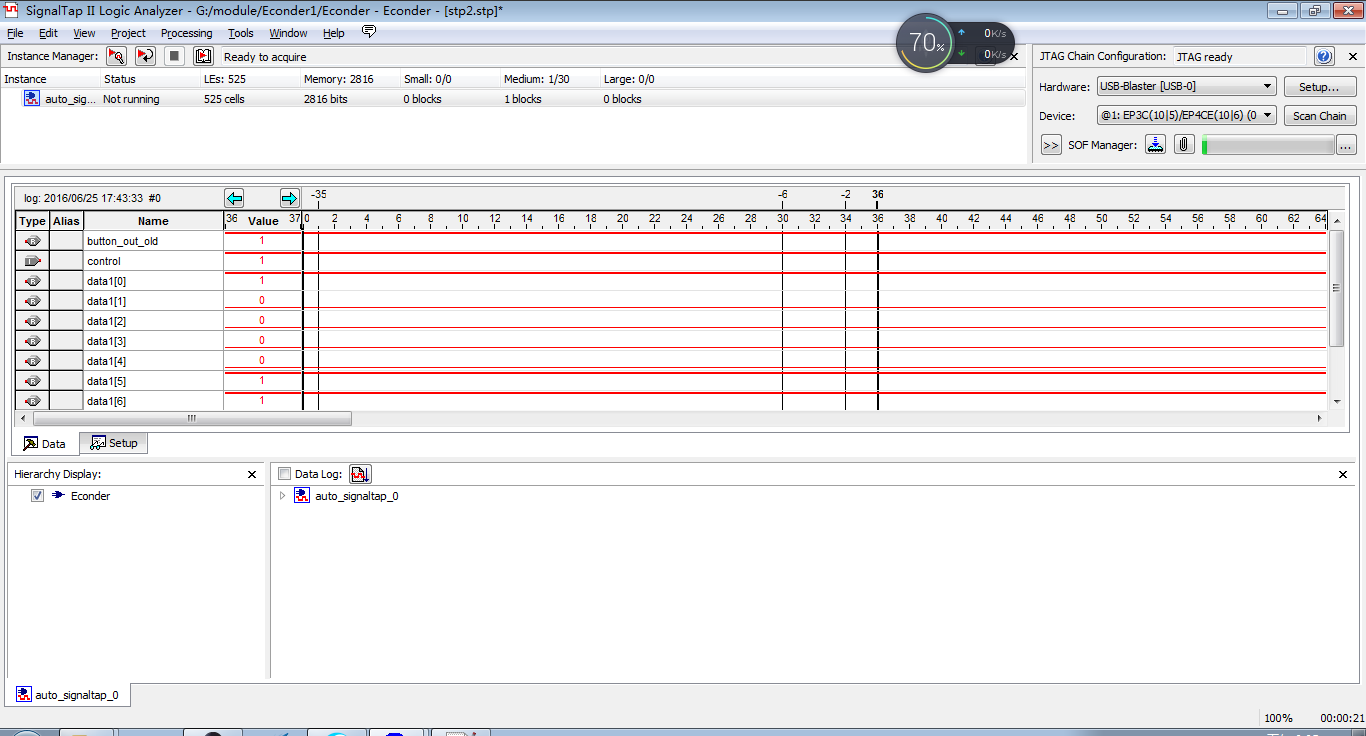

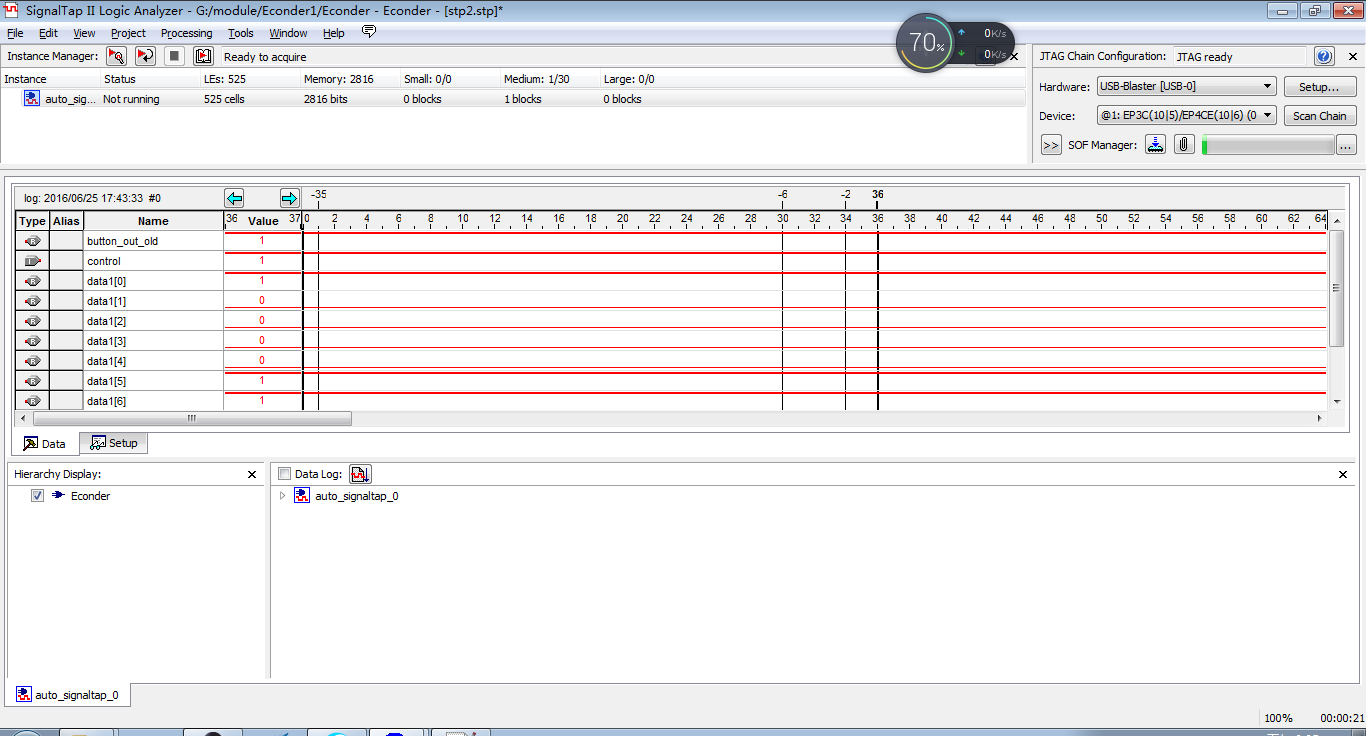

逻辑分析仪把端口加进去了没数据显示出来怎么办

数据显示出来了,但是数据不动弹,那个触发级我不知道选什么啊

没有图指导不了啊, 你是xilinx还是altera的啊

问题不详细

altera,现在调出来有波形了,不过显示前面一段后面的就不显示了是怎么回事呢?

谢谢您,我在后面贴出了我的问题,之前是我没把时钟信号添加上去,再者我后面的触发级选项应该怎么选呢,因为我的程序没有复位信号,初值都是下板子后默认值,波形图后面出来了,但是动了一下就没反应了。估计和你程序有关。

应该是你的设计有关。另外,采集的深度也要看一下设置的什么

我把我的程序附上来您看下,能不能指导我一下。

您能给个邮箱联系方式吗?我这是真遇到问题了。能不能请您指导一下

代码附不上来,而且下载到芯片上面是正确的,有点小问题想用逻辑分析仪看一下可以在程序中根据时钟频率做一个十几秒的计数器,等到计数增加到期望的值以后,产生一个拉高的start信号,在程序中把这个start信号作为整个系统功能的启动信号,signaltap触发这个start信号就可以抓取到程序的波形。

好的,谢谢,能给个邮箱吗?如果不行是否还能请教下?

您好,我的波形是出来了,但是只有当前触发的波形,之前的都没了是为什么呢

之前的肯定没有了啊,这是程序正常跑并不是仿真。建议做个定时,到时候用定时信号触发,深度稍微深点,单次触发就能看到你想看到的波形