脉冲同步器中的切换电路搞不懂

时间:10-02

整理:3721RD

点击:

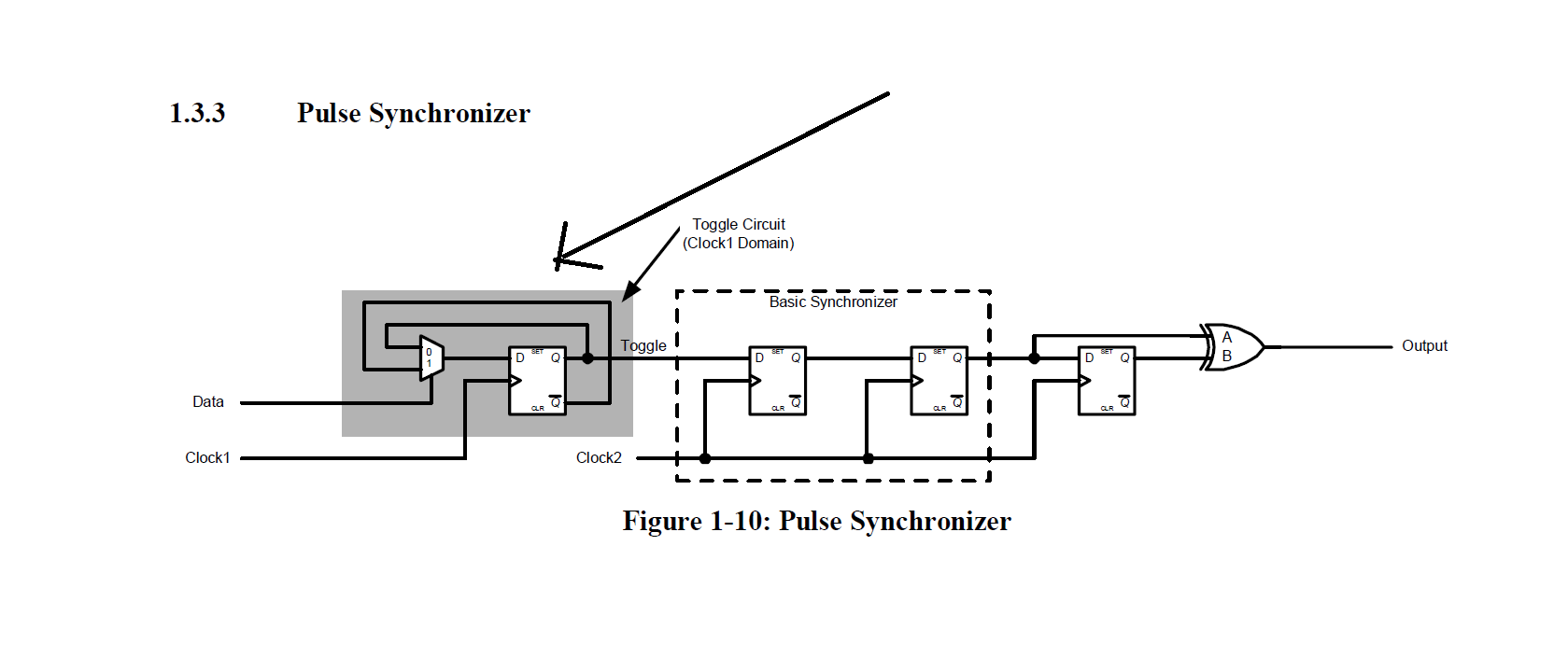

那一部分切换电路搞不明白,不知道怎么个切换法,用verilog如何描述,不懂再什么时候选择器输出什么

顶起来,同步这块,设计的类型太多,我都快搞糊涂了

就一T触发器,输入为“1”,输出就翻转。所以Datain为一脉冲信号,宽度为1CLK1周期,代表事件发生,导致D触发器输出翻转,延迟3拍CLK2后,异或输出1个CLK2周期的脉冲信号。

这是由快到慢的电路,这种电路实际上增加了时钟周期,以每个边沿扩大,在前面时钟f_clk时,当每个信号为1电平时,才会发生一次改变,只要脉冲信号相隔够远,就会被慢时钟s_clk采集到,在慢时钟如何分辨为一个脉冲呢,只要保证前一个时钟与后一个时钟的信号亦或为1即可,否则不是脉冲。我不知道讲的清楚吗,理解万岁。