Vivado在实现阶段怎么才能保证模块逻辑在布局布线前资源不被优化

2、在Vivado综合和实现时,模块综合后没有被优化掉,但是在实现(Implementation)阶段,进行的第一步逻辑优化(Opt-design)后大部分资源被优化掉,从而在布局布线后,得出来的资源利用率分析报告是不正常的,逻辑资源利用很少。

现在的问题是,为什么在ISE里面综合和实现后得出的资源利用分析报告是符合要求的,资源利用也正常,但是在vivado里面综合是正常的,实现阶段却有大部分资源都被优化掉?同一个工程,且约束文件都是各自对应所要求的约束,管脚分配也对。哪位大神之前也遇到过类似的情况,能否给小弟指点一下啊?万分感谢!

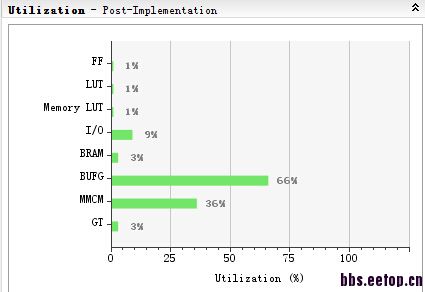

下面两个图是在Vivado综合和实现时分别得出的资源利用率分析图

应该是两个工具的选型设置不一样,vivado中对用户开放的选项少了很多。另外要看一下告警,是不是有逻辑被优化掉了。ISE中有个Trim unconnect net的选型确认一下有没有勾选上。

在ISE里面综合和实现都没问题,最后得出来的资源利用分析报告也是正常的。现在在Vivado里面,可以确定就在实现(implementation)的第一步进行逻辑优化(opt_design)把很多模块资源给优化掉了(提示说逻辑单元没有负载),但是在ISE实现的时候没有被优化掉,现在真的不知道问题到底出现哪了?

那你看一下我说的ISE里面的选型,这个勾掉的话你说的这种情况资源也会被优化掉的。

ISE里的Trim unconnect net的选型确实是勾选上。但是ISE实现后的资源利用是对的,基本符合设计的要求,没有太多的资源被优化。现在的问题是在Vivado里面综合后的资源利用也是正常的,优化的不是太多,但是实现阶段的第一步,逻辑优化后有很多资源被优化掉了,最后的资源利用很少,肯定不正常的,不应该用了那么少的资源。上面的两个图分别是vivado综合后和实现后的资源利用分析报告图,很明显看出来实现后很多资源被优化掉了!我由于刚接触vivado没多久,现在不知道该如何解决了,请问,您之前用vivado出现过类似的问题吗?非常感谢你上面对我的指点,我给你发了短信息,上面有我的QQ号,就是想以后咱们学习vivado多探讨,多交流,再次谢谢你了!

vivado我们已经用了很久了,没有遇到过你说的这种情况

从目前的情况分析,应该是你代码的问题。

vivado这个工具比ISE在语法方面要求更严格了。

看一下你的代码是不是严格按照语法写的。

另外,我没有时间上qq。不好意思

非常感谢你的回复,我的这个工程最开始的ISE的工程,后来为了验证vivado的效率能够提高多少,就直接把这个工程通过vivado里面的导入ISE工程的方法直接导入到vivado里面了,当然约束文件肯定得重新写的,这个我都弄好了,其它的vivado与ISE的代码风格和语法差别还有吗?我现在还不是很熟悉vivado,现在在vivado跑综合是没有问题的。

如果你想让某一个module或者信号不被优化,可以在module或者信号后面加/*synthesis keep_syn = 1*/

谢谢你的回复!你说的防止被优化的办法主要是针对综合阶段的,但是我现在综合阶段是正常的,没有太多的资源被优化,符合设计的要求,问题在于实现阶段,很多资源都被优化掉了,到现在还没解决这个问题

请问你的问题解决了没有啊,最终如何处理的?

这个问题我也遇到过, 最后还是代码的问题, 有的信号 或者模块 没有负载的话 就会被完全优化掉

多谢分享,学习中