请教下,关于用verilog实现一个从2开始的模8计数器

时间:10-02

整理:3721RD

点击:

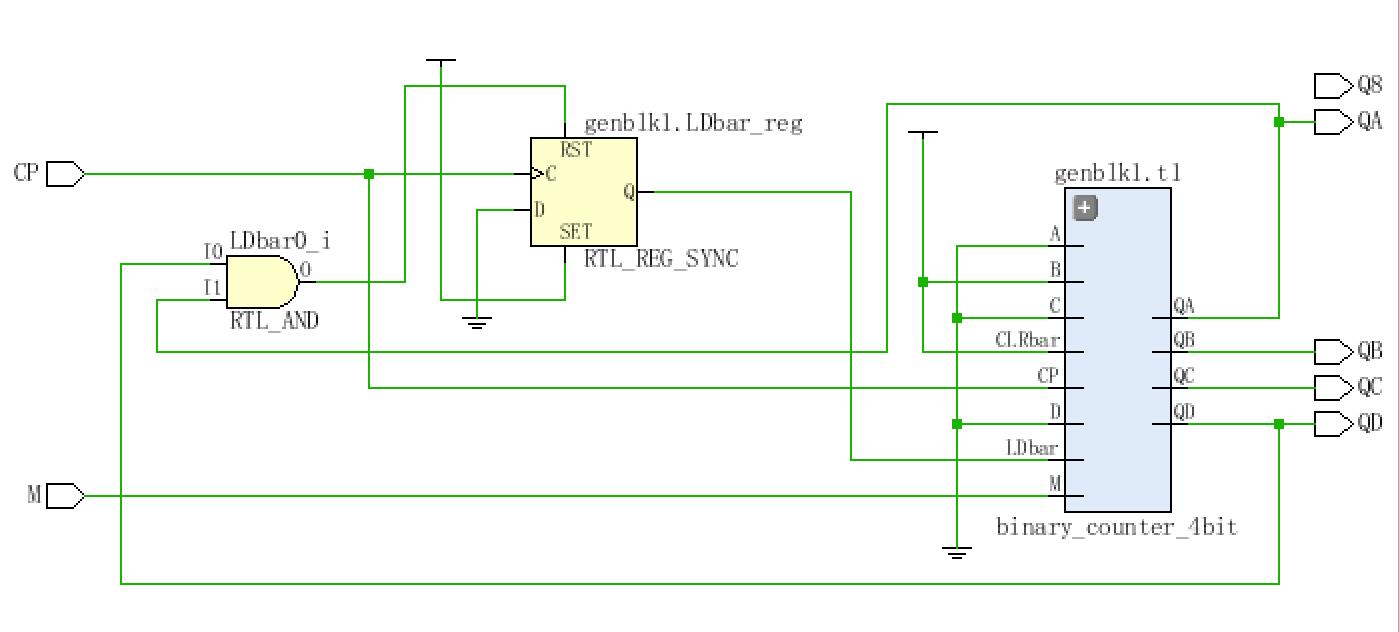

这是利用一个4位二进制计数器实现一个从2开始的模8计数器。

关于4位二进制计数器的端口说明:

1.QD,QC,QB,QA为输出计数值

2.ABCD为预制初值

3.LDbar=0时,QD=D,QC=C,QB=B,QA=A

4.CLRbar=0时,QD,QC,QB,QA都为0。

这个模8计数器,从2开始计数到9就跳回2,Q8为从9到2时输出一个负脉冲。

而现在问题是,我的模块代码如下,生成的电路图并Q8端口并没有连在电路上,

按理来说,应该条件语句中给他赋值了,应该就会有导线连在Q8了吧?

请大家帮忙分析下,谢谢!

- module octal_counter(

- input CP,M,

- output QA,QB,QC,QD,Q8

- );

- begin

- reg A,B,C,D,LDbar,CLRbar,Q8;

- initial

- begin

- A<=0;

- B<=1;

- C<=0;

- D<=0;

- CLRbar<=1;

- LDbar<=1;

- end

- //LDbar=0时,QD=D,QC=C,QB=B,QA=A

- binary_counter_4bit t1(A,B,C,D,M,LDbar,CLRbar,CP,QA,QB,QC,QD,QCCbar);

-

- always @(posedge CP)

- begin

- if(QD&&QA) //当QDQCQBQA=1001时,恢复预设值ABCD

- begin

- Q8=0;

- LDbar=0;

- end

- else

- begin

- Q8=1;

- LDbar=1;

- end

- end

- end

- endmodule