Verilog语言问题

时间:10-02

整理:3721RD

点击:

急需!在实现一个模块框图时,但是需要三个流程图,一个读过程,一个写过程,一个控制读写过程,如果三个过程都采用状态机实现,那么在一个模块中是需要每个过程都单独用parameter定义状态,还是所有状态放在一起用一个parameter定义。谢谢大神们!

可以把具体模块框图贴出来看看

建议分开做,方便后续增加一些功能,调试都会比较方便

你如果是三个独立的状态机,肯定是分别单独定义了,这样清晰明了,搅在一起不是自找麻烦么

分开的模块,为了方便还是分开的好

恩,谢谢

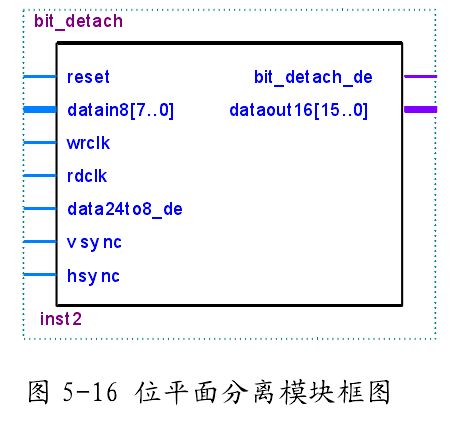

这个是框图

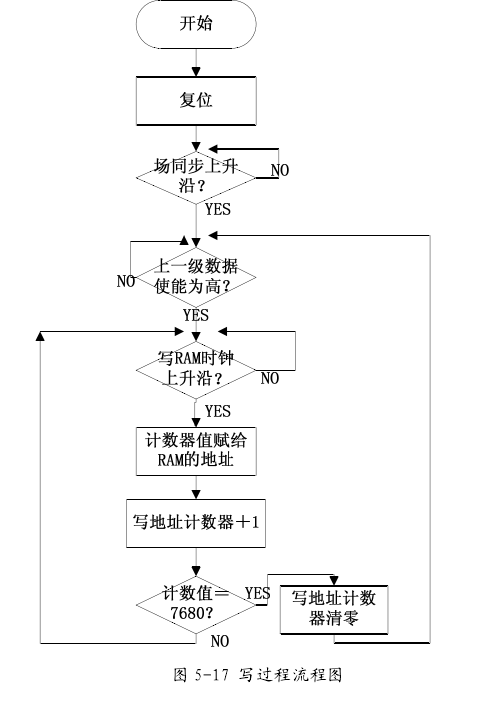

这个是写过程流程图

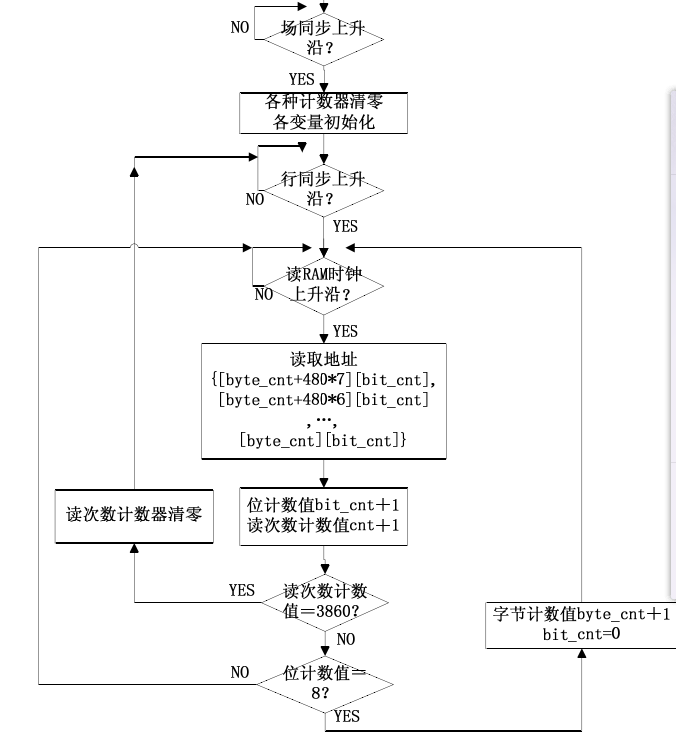

这个是读过程流程图

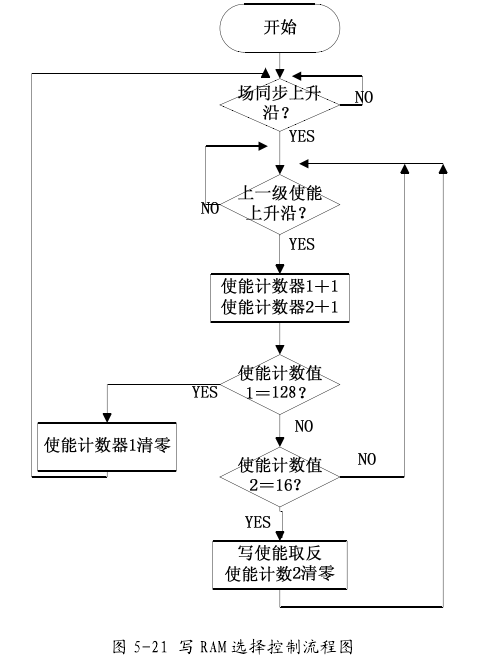

这个是选择流程图

我在下面发了框图,和过程流程图,是利用双口RAM 缓存源视频解码后的RGB数据,后面数据再存入SRAM中,能帮我看看吗?谢谢

我贴出了框图和流程图,能帮我看下吗,谢谢。分开好啊,互相不影响

顶层模块下面调用这三个并列子模块。

接下来的事情就是分别定义它们,依靠接口参数的输出输入来trigger它们。

框图画的这么清楚,应该很好写。

这个RAM模块只是整个工程里面的一个模块,不是顶层模块,你的意思是顶层模块下还可以再定义顶层模块?

我的意思这三个模块相对独立的,没必要共用状态机。

你可以参考下面链接中我写的代码。

http://bbs.eetop.cn/viewthread.p ... p;extra=&page=5