串口数据发送遇到的问题

module control_module

(

clk_a,RSTn,

TX_Done_Sig,

timer1s,

Data_out,

TX_En_Sig,TX_Data

);

input clk_a;

input RSTn;

input TX_Done_Sig;

input timer1s;

input [47:0] Data_out;

output TX_En_Sig;

output [47:0] TX_Data;

reg isEn;

reg [47:0] rData;

always @ ( posedge clk_a or negedge RSTn )

begin

if ( !RSTn )

begin

isEn <= 1'b0;

rData <= 0;

end

else if ( TX_Done_Sig )

begin

isEn <= 1'b0;

end

else if ( timer1s ) //1s定时到,统计量Data_out传递给rData用于串口传输

begin

rData <= Data_out;

isEn <= 1'b1;

end

end

assign TX_Data = rData;

assign TX_En_Sig = isEn;

endmodule

else if ( TX_Done_Sig )

begin

isEn <= 1'b0;

end

没有抓取 其次跨时钟域看看

如果 TX_Done_Sig 信号一直为1'b1的话,那是进不了下面的。

timer1s和Data_out没有重合的地方,你的data_out应该是用timer1s打出来的吧,你后面又用timer1s作为有效信号去采样data_out,当然采不到啊。

你可以把timer1s打一拍。

always @ ( posedge clk_a or negedge RSTn ) begin

if(!RSTn) timers1s_reg <= 'b0;

else timers1s_reg <= timers1s;

end

然后用timers1s_reg作为valid信号去采样data_out.

else if ( timer1s_reg ) //1s定时到,统计量Data_out传递给rData用于串口传输

begin

rData <= Data_out;

isEn <= 1'b1;

end

end

Tx_Done信号已经抓取,不可能一直为正,因为我的串口是发送成功的!而且是每秒发送1次,没问题的这点!

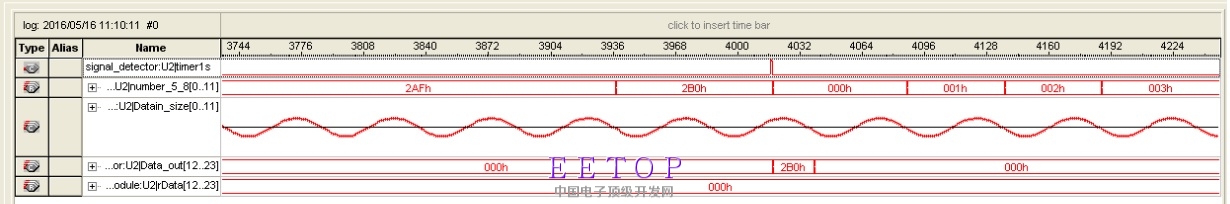

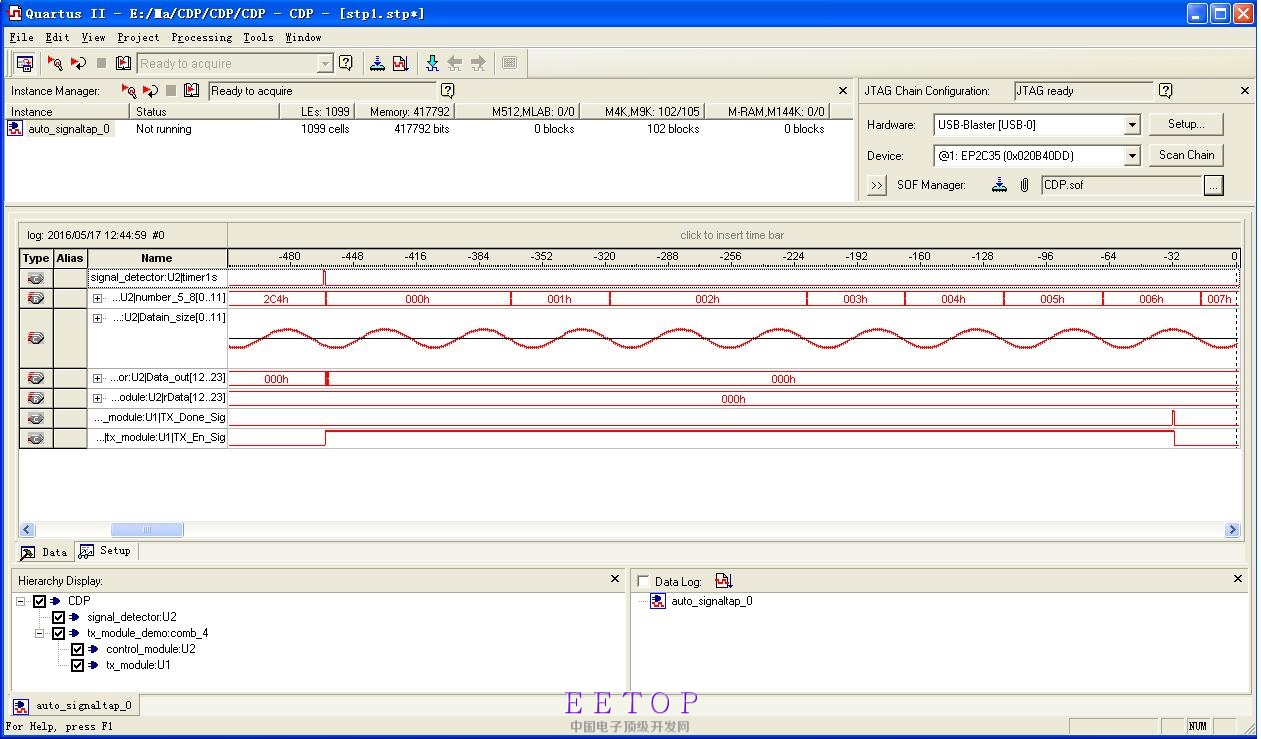

感谢回复,按照您的方法进行修改验证,发现问题依旧,我把SignalTap II看到的信号截图上传上来。

放大timer_1s那个点的波形,我初略看,在timer_1s那个周期,data_out的数据好像就是 0,你check一下

Data_out刚好是在timer1s从高转低时刻,出现数据!所出数据具体数值即为number5_8这个数值。

那你觉得这样 rData 能采到 Data_out 的数据吗?

这样是采不到的啊!Data_out 在 time_1s 后面1个周期,这怎么采。

那我应该怎么样才能采到?延迟半个周期再采集?

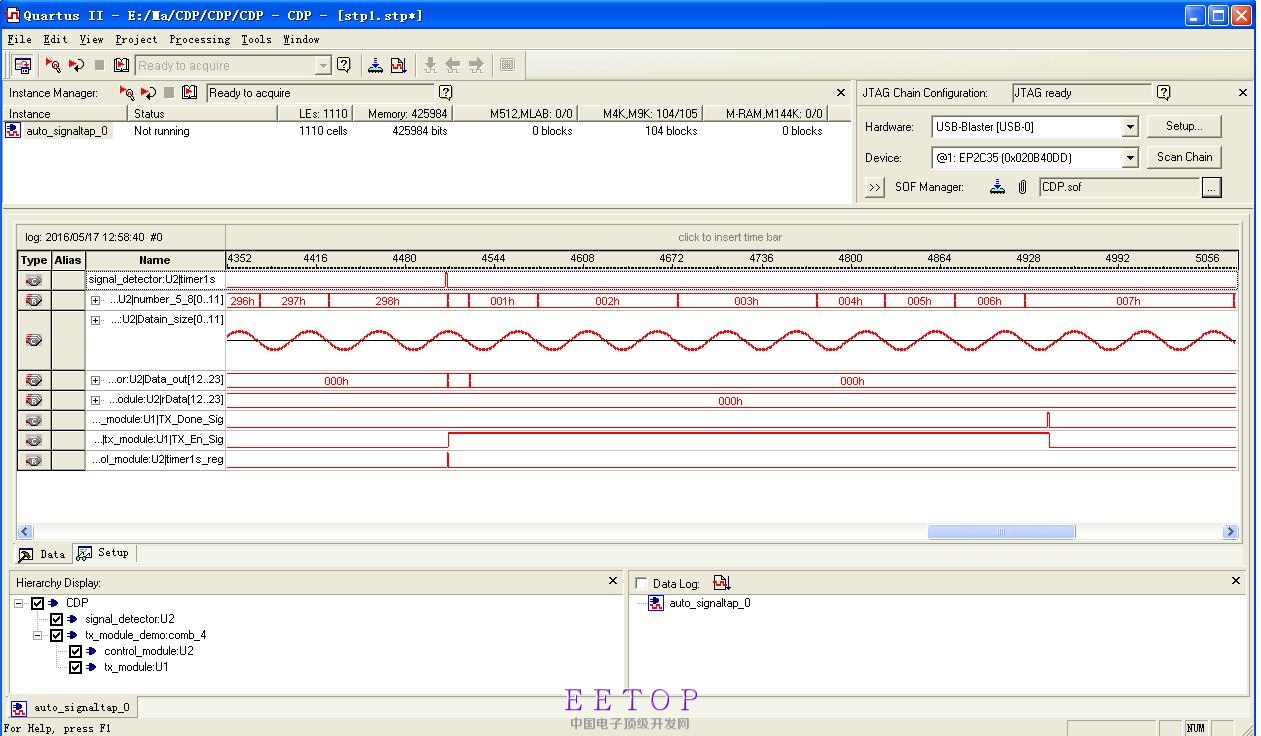

你应该延时time_1s一个周期采样才行吧。

你要确保time_1s和你要采样的数据时对其的啊,也就是同一个cycle里面,两者都有效!

你好!很感谢回复。我后来引入tiemr1s_reg作为变量传递的有效信号(根据3楼的回复),可是即使引入这个触发信号,相当于延时一个时钟,可是结果依旧没变化啊?为什么?

用timers1s_reg作为valid信号去采样data_out.

else if ( timer1s_reg ) //1s定时到,统计量Data_out传递给rData用于串口传输

begin

rData <= Data_out;

isEn <= 1'b1;

end

end

你能把你模块的时钟clka和复位都拉出来看看么。然后再把timer_1s有效的地方放大看看,参照时钟信号看看时序