毕设设计16阶FIR滤波器问题遇到系统响应系数如何导入电路中

时间:10-02

整理:3721RD

点击:

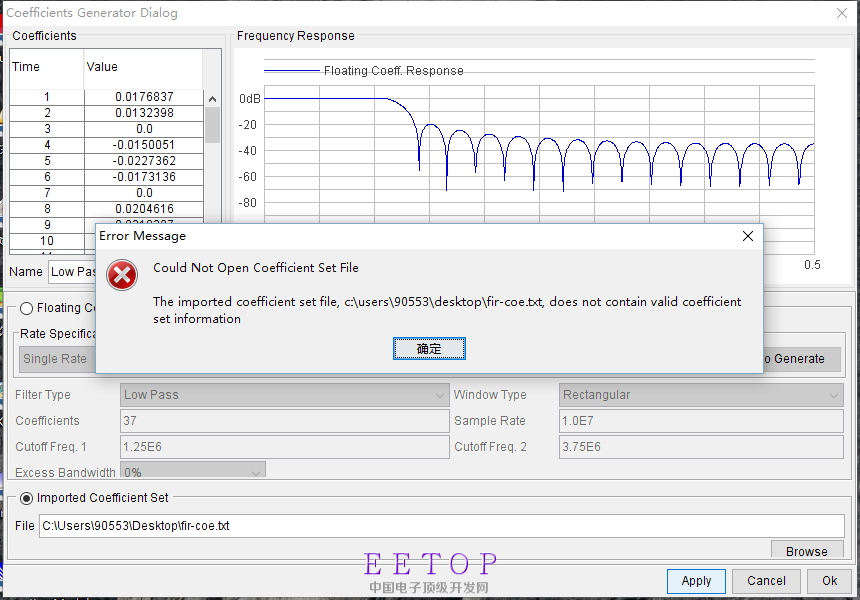

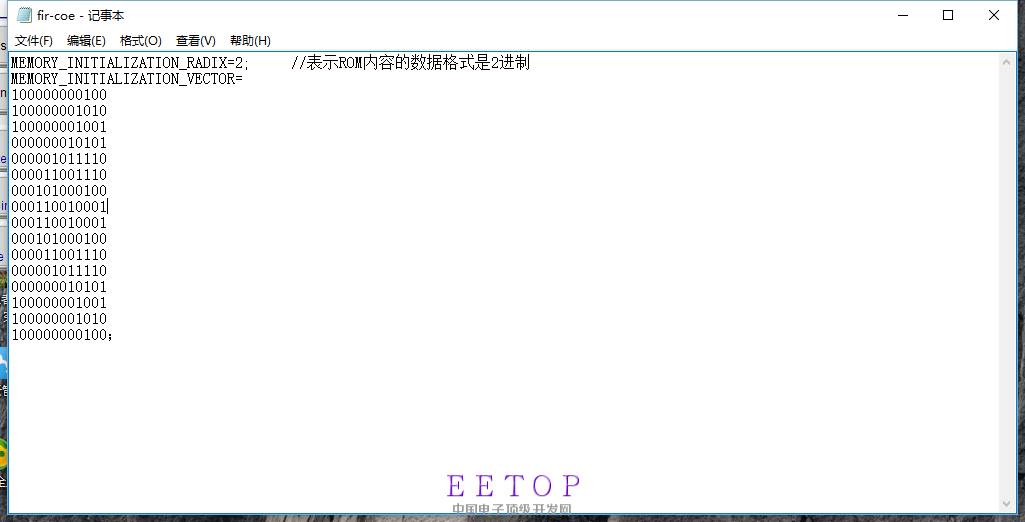

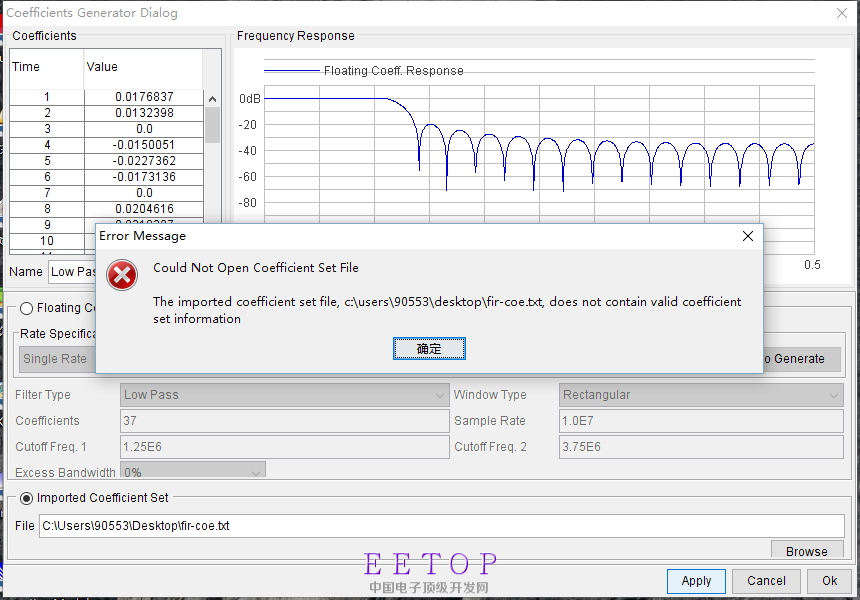

求助前辈,我用MATLAB的FDTOOL设置参数获取了系数并量化成二进制,滤波器是划分成几个模块单元用VHDL写的,然后连接起电路图。但是遇到的问题是我不知道怎么导入系数到IP核里面,仿真时每个乘法器用各自的系数与输入相乘,在网上看了攻略贴,有的说建立个TXT文件拷入系数然后用QUartus2中的IP核界面导入,但是我导入时Quartus2不识别见图[attach]655972[/attach][attach]655971[/attach]

图片挂了好像,第一次发帖。

如果直接用这个界面上的平台设计滤波器得到系数又怎么在电路仿真中使用呢?

急急急!在线等

系数采用十进制;

直接按结构编程呢?