Spartan 3AN DCM原语使用的问题

- DCM_SP #(

- // .CLKDV_divIDE(2.0), // Divide by: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5

- // 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 or 16.0

- .CLKFX_divIDE(1), // Can be any integer from 1 to 32

- .CLKFX_MULTIPLY(4), // Can be any integer from 2 to 32

- .CLKIN_divIDE_BY_2("FALSE"), // TRUE/FALSE to enable CLKIN divide by two feature

- .CLKIN_PERIOD(0.0), // Specify period of input clock

- .CLKOUT_PHASE_SHIFT("NONE"), // Specify phase shift of NONE, FIXED or VARIABLE

- .CLK_FEEDBACK("1X"), // Specify clock feedback of NONE, 1X or 2X

- .DESKEW_ADJUST("SYSTEM_SYNCHRONOUS"), // SOURCE_SYNCHRONOUS, SYSTEM_SYNCHRONOUS or

- // an integer from 0 to 15

- .DLL_FREQUENCY_MODE("LOW"), // HIGH or LOW frequency mode for DLL

- .DUTY_CYCLE_CORRECTION("TRUE"), // Duty cycle correction, TRUE or FALSE

- .PHASE_SHIFT(0), // Amount of fixed phase shift from -255 to 255

- .STARTUP_WAIT("FALSE") // Delay configuration DONE until DCM LOCK, TRUE/FALSE

- ) DCM_SP_inst (

- .CLK0(CLK0), // 0 degree DCM CLK output

- // .CLK180(CLK180), // 180 degree DCM CLK output

- // .CLK270(CLK270), // 270 degree DCM CLK output

- // .CLK2X(CLK2X), // 2X DCM CLK output

- // .CLK2X180(CLK2X180), // 2X, 180 degree DCM CLK out

- // .CLK90(CLK90), // 90 degree DCM CLK output

- // .CLKDV(CLKDV), // Divided DCM CLK out (CLKDV_divIDE)

- .CLKFX(iCLK), // DCM CLK synthesis out (M/D)

- // .CLKFX180(CLKFX180), // 180 degree CLK synthesis out

- // .LOCKED(LOCKED), // DCM LOCK status output

- // .PSDONE(PSDONE), // Dynamic phase adjust done output

- // .STATUS(STATUS), // 8-bit DCM status bits output

- .CLKFB(CLK0), // DCM clock feedback

- .CLKIN(CLKIN), // Clock input (from IBUFG, BUFG or DCM)

- // .PSCLK(PSCLK), // Dynamic phase adjust clock input

- // .PSEN(PSEN), // Dynamic phase adjust enable input

- // .PSINCDEC(PSINCDEC), // Dynamic phase adjust increment/decrement

- .RST(iRSTn) // DCM asynchronous reset input

- );

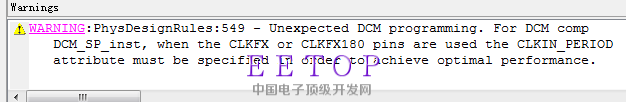

产生的警告如图,求告知原因。

为什么不用图形配置界面?

请问一下,是高手们都喜欢用Schematic输入的方式吗?我很少用。

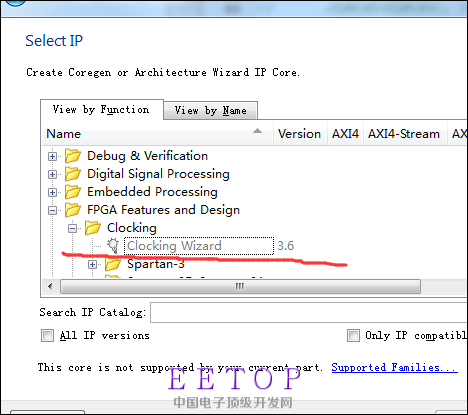

不是Schematic方式,是DCM的clocking wizard,也就是core generator,图形配置界面,生成.v文件后,直接调用。

你这个.v应该也是core generator生成的,是因为.CLKIN_PERIOD(0.0), // Specify period of input clock,你的输入时钟的周期没有指定。

如果使用core generator,这里会自动填入你指定的周期值的,比如.CLKIN_PERIOD(20.0), // Specify period of input clock

另外,建议DCM的输入时钟要经过IBUFG,输出要经过BUFG,FB也要经过BUFG,这样才是DCM完整的应用。

感谢您的回复,这个我没用过……是跟IP核是一个东西吗?

这句话超赞!我也是最近才知道的,所有时钟都要经过DCM。

"建议DCM的输入时钟要经过IBUFG,输出要经过BUFG,FB也要经过BUFG,这样才是DCM完整的应用。"

不能用……

你用的FPGA的详细型号是什么?

Spartan3AN,xcs700AN,FGG484

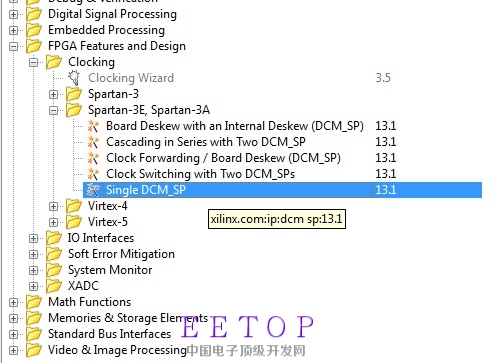

可以的,用这个:

生成的.v文件为:

module clk4out(CLKIN_IN,

RST_IN,

CLKFX_OUT,

CLKIN_IBUFG_OUT,

CLK0_OUT,

LOCKED_OUT);

input CLKIN_IN;

input RST_IN;

output CLKFX_OUT;

output CLKIN_IBUFG_OUT;

output CLK0_OUT;

output LOCKED_OUT;

wire CLKFB_IN;

wire CLKFX_BUF;

wire CLKIN_IBUFG;

wire CLK0_BUF;

wire GND_BIT;

assign GND_BIT = 0;

assign CLKIN_IBUFG_OUT = CLKIN_IBUFG;

assign CLK0_OUT = CLKFB_IN;

BUFG CLKFX_BUFG_INST (.I(CLKFX_BUF),

.O(CLKFX_OUT));

IBUFG CLKIN_IBUFG_INST (.I(CLKIN_IN),

.O(CLKIN_IBUFG));

BUFG CLK0_BUFG_INST (.I(CLK0_BUF),

.O(CLKFB_IN));

DCM_SP #( .CLK_FEEDBACK("1X"), .CLKDV_divIDE(2.0), .CLKFX_divIDE(1),

.CLKFX_MULTIPLY(4), .CLKIN_divIDE_BY_2("FALSE"),

.CLKIN_PERIOD(20.000), .CLKOUT_PHASE_SHIFT("NONE"),

.DESKEW_ADJUST("SYSTEM_SYNCHRONOUS"), .DFS_FREQUENCY_MODE("LOW"),

.DLL_FREQUENCY_MODE("LOW"), .DUTY_CYCLE_CORRECTION("TRUE"),

.FACTORY_JF(16'hC080), .PHASE_SHIFT(0), .STARTUP_WAIT("FALSE") )

DCM_SP_INST (.CLKFB(CLKFB_IN),

.CLKIN(CLKIN_IBUFG),

.DSSEN(GND_BIT),

.PSCLK(GND_BIT),

.PSEN(GND_BIT),

.PSINCDEC(GND_BIT),

.RST(RST_IN),

.CLKDV(),

.CLKFX(CLKFX_BUF),

.CLKFX180(),

.CLK0(CLK0_BUF),

.CLK2X(),

.CLK2X180(),

.CLK90(),

.CLK180(),

.CLK270(),

.LOCKED(LOCKED_OUT),

.PSDONE(),

.STATUS());

endmodule

直接把这个.v文件例化到你的设计中。

感谢您细心耐心的回复,顺便问一下,1.“ LOCKED_OUT”信号究竟有什么用啊,是不是不需要也行,2.实际中,我只需要输出CLKFX_OUT就够了,其他输出就不用实例化了吧?

lockedout信号是时钟锁定,当输出时钟稳定后,这个信号拉高,可以把这个信号当做你的系统复位。

就按着生成的模块例化,不用的信号放在那不用就是了。

懂了,LOCKED_OUT就是用来观察输出时钟稳定了没有。再次感谢您的耐心回答,很受用!