让人蛋疼的Xilinx->ISE->XST综合器,看到这个结果哥Hold住了!

问题1:所有的单端口RAM全部综合出错,写完再读出来全是0。同样是RAM模型,别的综合工具怎么就没问题?换了IP就行了。

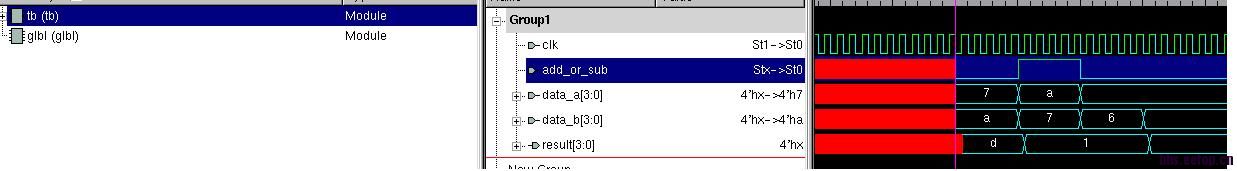

问题2:有关加法器的问题,大家请看以下代码:

module add_sub(clk,add_or_sub,data_a,data_b,result);

input clk;

input add_or_sub;

input[3:0]data_a;

input[3:0]data_b;

output[3:0]result;

reg [3:0]result;

always @(posedge clk)

if(add_or_sub)

result<=data_a+data_b;

else

result<=data_a-data_b;

endmodule

我的本意这是一个有符号数的加减法器,这里不考虑溢出的问题,实际中不会溢出。其实加法器无所谓有符号还是无符号,只要以补码形式就都能兼容。比如“0111”+"1010",以无符号数算是7+10=17,取低四位是1,完全正确(溢出不考虑)。如果是有符号数就是(+7)+(-6)=1,也完全正确!对于减法实际还是用加法实现的,只要把被减数按位取反再加1即可。因此像Syn Pro以及QuartusII的综合器都是用一个二选一选择器实现,一路是两个数直接加,另一路是data_b按位取反再加1后再和data_a相加。可是狗血的XST综合后加法功能正确减法就不对!非要将申明成“input signed [7:0]data_a----"减法功能才正确。不都是支持Verilog-2001的吗?为什么差距这么大?在此B4一下Xilinx!用的ISE软件版本是10.1。

synpro转ISE

我做过xilinx到lattice的移植,确实很头疼。XST跟其他综合器的要求是不一样的。例如说,xilinx下的通过variable的方式用TO_X01(INIT)方式复位在lattice下不可行。

XST没有错误,你做的是网表仿真,里面有glbl,glbl会有一段系统复位时间。在这段时间内,不管你输入什么,输出都是0,一旦过了这段时间,结果就是对的。

一定要hold住。

楼上,说错误是我们同事告诉我的,当时应该是行为级仿真,这个明天确认一下!但是我的确看到,你要不申明是有符号的,在RTL-VIEW里用的是无符号加法器,如果申明是有符号的用的就是有符号加法器!还有不知道你用的ISE是什么版本,今天我用12.1综合看了一下RTL级用的又是加减器实现的。

RTL仿真与你用什么综合器没有关系啊,ps:我用的是ISE10.1,你发的RTL我没有更改。

今天确认了第二个问题是我同事弄错了,她自作主张把output[3:0]result;

改成了output[4:0]result;

扩展一位,如果不申明成signed型减法就错了。

第一个问题是千真万确的错了!

呵呵,Xilinx是不大可能出错的,出错了,还是找自己的原因比较好

第二个问题是我没把好关,但第一个问题怎么解释?怎么不出错?考,单端口RAM就错了!千真万确!,用syn pro 综合就不错!用altera自己的综合器也不错!如果ISE你不能综合那你报错啊,一个警告都没有!那个ram的模型是IC foundry 提供的,我的500万门的ASIC就用的是这个模型!楼上的哪个软件都不可能没有bug!MS还天天打BUG呢!切

软件是有bug,但那种bug不会出现在这种基本问题上,大多出现在ip(不是ram,而是ddr,pcie等IP),

如果你是用rtl推断出ram,一定要按照相应综合器的语法例子(xst有xst的语法,synplify有synplify的语法),还有就是ram的结构。 不要动不动就怪综合器。那个ram文件没有更新,那是因为你没有按照操作要求做。

各家有各家的要求,这个你不用说我也知道,打开文档肯定都有例子,我要从头开始看文档按照他的规则来,肯定也不会出问题。但我的设计已经全部自主化了,跨平台就应该能用,大家都是遵从同样一个语法规则,其他两家的都没有问题,用syn选择xilinx平台综合更没有问题,那是为什么呢?那我只能说你软件的兼容性完备性不够好!如果说我的写法你不能综合或者没按照你的规则来,你报错,你警告啊!但是一个也没有。这就是让人蛋疼的地方,最后只能层层debug才定位到单端口RAM的问题。

这点我比较认可,最好找xst的help来看一下,里边有介绍怎么按照他的意思去写ram。

小编好厉害啊,学习

用Xilinx的加法器。避免因不同器件造成的加减法的区别。

能不用IP就不用IP,这是我做FPGA及ASIC这8年来的经验。读研时我做了Viterbi译码器,当时IP还是要钱的,如果要用得付1.5万美金,幸亏有了自主的设计,后来我们的基带ASIC化的时候没有卡壳的地方。再后来我做了若干信号处理的电路,当时虽然已经Verilog化,但是还是喜欢例化各家的功能库。后来发现如果有需要将设计向Xilinx平台移植时发现,要改的地方还不少。因此在做我的第一个SOC的时候痛下决心,设计一定要自主化,加减法器,乘法器,RAM,FIFO等等。这一次真有需要向Xilinx平台移植时,代码原封不动就过来了,只可惜刚来的同事还不会用第三方的综合工具,否则移植一次成功的。

是的,PLL肯定没办法必须用,包括一些clk gate控制,latch等最好还是用器件的。至于RAM本人持保留态度,明天把这段代码贴出来,大家看看为什么他就不能综合。遇到问题的确得淡定,万事皆有因,这是本人在单位归了若干零(航天的术语归零就是出了问题找原因)得出来的结论。无论是硬件的还是软件的。碰到问题不可怕,寻找问题的过程肯定也很难受,但是当你找出原因后哪种顿悟和释然是很爽的。这回这个项目是有太急了,就给4天时间(除了我的部分还有其他的部分)整机调试,然后要去外单位联试,时间不等人啊!研究所都这德性,硬件生产焊接时间长,留给软件的时间很短。

RAM写完是不是会保持啊

ram必须用IP,除非你非常清楚综合器的行为,会将哪些综合成RAM,哪些直接用FF。

当然,ip也要先做一下验证,看看行为。

RAM必须用IP?好像不必吧,syn 都推荐大家自己写!

顶楼上,更多的时候还是先把自己的问题确认清楚。

呵呵,工具都很傻的

坐着看你们讨论

我也相信软件有bug,但是基本问题不要怀疑软件 一些不常用的设置软件就不可靠了

呵呵,Xilinx是不大可能出错的,出错了,还是找自己的原因比较好

膜拜LZ

非常感谢你,非常好

看了收益匪浅啊

如果用Xilinx的FPGA,个人认为最好用synplify_pro综合,更专业!

博主上海那家院的吗?