数据传递

时间:10-02

整理:3721RD

点击:

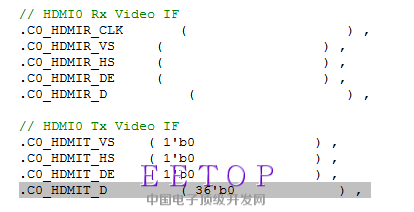

输入数据HDMIR0_D经过一系列的传递,得到输出数据HDMIT0_D.除了CO_HDMIR_D,CO_HDMIT_D,其他各步之间的传递都是明确的赋值过程(例如r_hdmit0_d <= r_c0_hdmit_d_3d),

而CO_HDMIR_D,CO_HDMIT_D之间是通过下图中的程序传递信息的。

我不明白的是,为啥括号里面啥都没有就能传递信息呢?请大神帮忙解决,谢谢!

你一定看错了,要不你仿真的库没有重新编译,和代码对应不上。

是不是systemverilog 写的?貌似systemverilog 端口名和信号名完全一样的时候可以省略,如果一个模块内全都一样都可以直接用 一个 .* 全省了

是在ISE上用Verilog写的

初学者一枚,不是太明白你的意思,能说详细一点吗 PS:在ISE上用Verilog写的

verilog时不能省的,那我也不知道为啥了。不过我看注释有个“IF” ,估计是interface的意思,而interface是systemverilog里的概念

好的,我再查一下IF。 谢谢!