ISE时序约束问题

时间:10-02

整理:3721RD

点击:

我用到的时钟结构为:IBUFGDS+PLL+BUFG的结构,利用内部晶振为200MHz的差分输出经过IBUGFDS,在经过PLL分频为50MHz的输出,PLL的输出再接BUFG缓存。50MHz的时钟做为FPGA的全局时钟信号。我的约束如下:NET "CLK_IN1_N" TNM=CLK_IN1_N;

TIMESPEC TS_CLK_IN1_N=PERIOD "CLK_IN1_N" 5ns HIGH 50%;

NET "CLK_IN1_P" TNM=CLK_IN1_P;

TIMESPEC TS_CLK_IN1_P=PERIOD "CLK_IN1_P" 5ns HIGH 50%;

NET "CLK_IN1" TNM=CLK_IN1;

TIMESPEC TS_CLK_IN1=PERIOD "CLK_IN1" 5ns HIGH 50%;

以上CLK_IN1_N和CLK_IN1_P为内部晶振的差分输入,CLK_IN为经过IBUFGDS后的信号,PLL的输出信号为clk_0,BUFG的输出信号为clk_1。跪求各位大神给以解惑,实在不懂这个约束怎么定义了。

TIMESPEC TS_CLK_IN1_N=PERIOD "CLK_IN1_N" 5ns HIGH 50%;

NET "CLK_IN1_P" TNM=CLK_IN1_P;

TIMESPEC TS_CLK_IN1_P=PERIOD "CLK_IN1_P" 5ns HIGH 50%;

NET "CLK_IN1" TNM=CLK_IN1;

TIMESPEC TS_CLK_IN1=PERIOD "CLK_IN1" 5ns HIGH 50%;

以上CLK_IN1_N和CLK_IN1_P为内部晶振的差分输入,CLK_IN为经过IBUFGDS后的信号,PLL的输出信号为clk_0,BUFG的输出信号为clk_1。跪求各位大神给以解惑,实在不懂这个约束怎么定义了。

就这样定义就可以了,PLL会把约束传递下去。

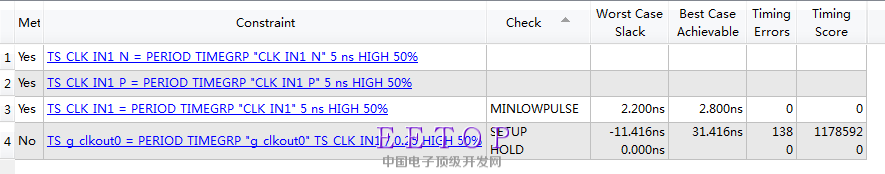

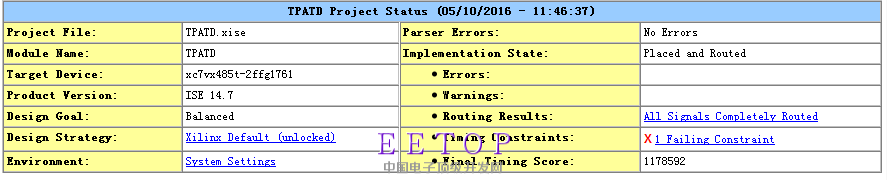

不行,错误截图如下 :

我是不是得把以下约束中的HIGH改为LOW?

NET "CLK_IN1_N" TNM=CLK_IN1_N;

TIMESPEC TS_CLK_IN1_N=PERIOD "CLK_IN1_N" 5ns HIGH 50%;

其实PLL传递的真实参考应该是:

NET "CLK_IN1" TNM=CLK_IN1;

TIMESPEC TS_CLK_IN1=PERIOD "CLK_IN1" 5ns HIGH 50%;

即使你的差分buffer部分不设置约束也没有关系的。

要检查一下你的PLL输出时钟驱动的逻辑中,最长的data path在哪里,这些fail的data path是什么引起的,如果是由于组合逻辑太长造成,就要加pipe line处理。

内部晶振是?

全局时钟?

觉得你约束的有点多,时序报错,要根据时序报告检查。