关于DDR3的读写操作,看看我的流程对吗?

2.等初始化完成后(即init_calib_complete为高电平)1.5s,对ddr3写操作,在app_wdf_rdy为高,且app_rdy为低电平时,使能app_en,且app_cmd=0;

3.判断:

a,若(app_rdy == 1) && (app_wdf_rdy == 1) ,则app_wdf_wren<=1, app_wdf_end <= 1 ,app_wdf_data=写数据,app_addr

<=初始地址,步骤4。

b,若(app_rdy == 0) && (app_wdf_rdy == 1) ,则app_wdf_wren<=0, app_wdf_end <= 0 ;等待app_rdy == 1。

c,若 (app_wdf_rdy == 0) ,返回2。

4.判断:

a,若(app_wdf_rdy == 1),则app_wdf_wren<=0, app_wdf_end <= 0 ,app_addr

<= app_addr + 8 ;步骤3;

b,( app_addr == ADDRESS ),ADDRESS为设定的最大地址值;步骤5;

c,若 (app_wdf_rdy == 0) ,返回2。

5.空闲40周期,步骤6;

6.读操作,判断:

a,若(app_addr == ADDRESS),读结束,步骤7;

b,若( app_rdy == 1),app_en <= 1 ;app_cmd

<= 3'd1,app_addr

<= app_addr + 4 ;步骤6;

c,否则,步骤6;

7.空闲1024周期,步骤3。

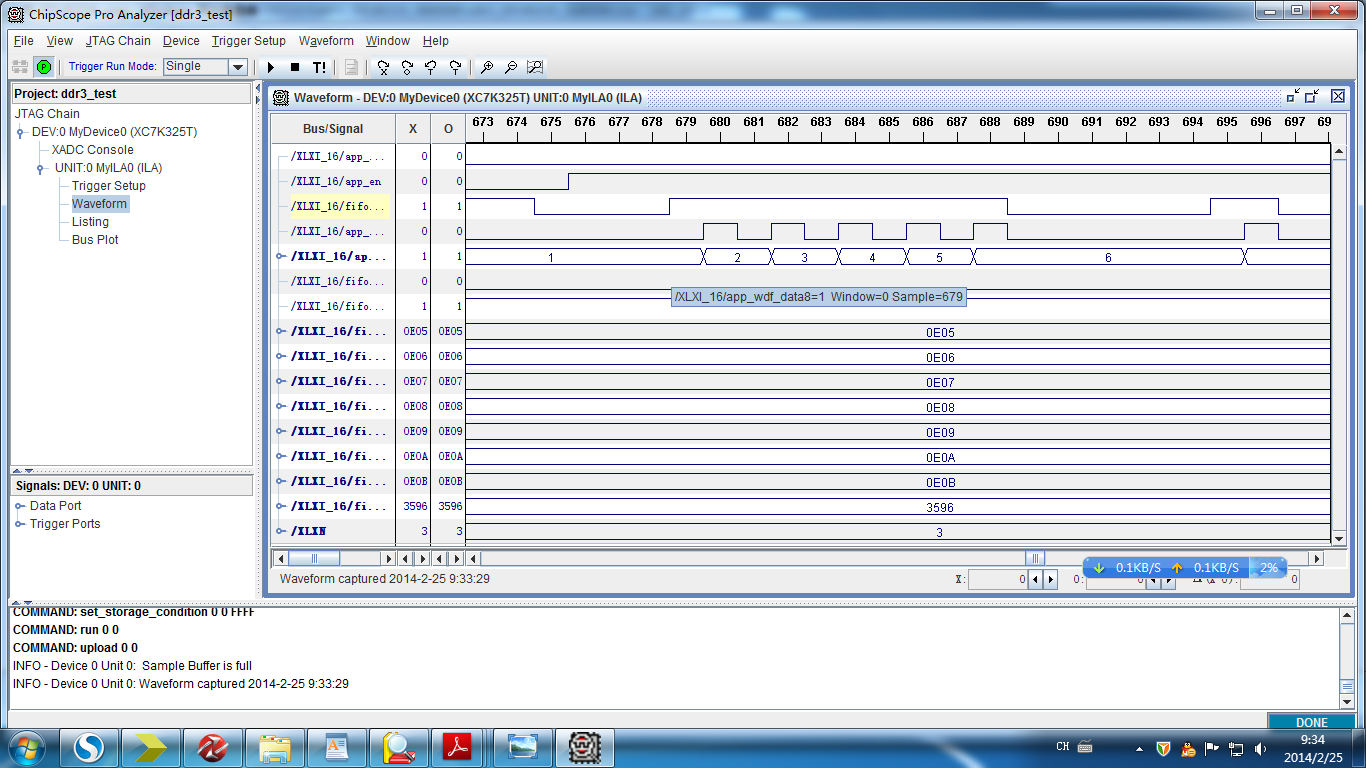

但是有时候读的数据不是写进去的数据,如图:[attach]572540[/attach]

步骤4.b中,app_en<=0,app_wdf_wren<=0, app_wdf_end <= 0 ,app_addr <= 0,步骤5

周一,会有人来解答的吧

结贴了,调差不多了。虽然没人回答,但是希望能对别人有点借鉴意义。我只能说调试别人是帮不了你的,逛逛论坛,启发一下倒是真的,一百个人调试,一百个不同的问题,让人怎么帮。

您好,我来晚了,呵呵!我最近也在kc705上做ddr3的实验,但苦于没人交流,你的ddr3调试成功了吗?

您好,我来晚了,呵呵!我最近也在kc705上做ddr3的实验,但苦于没人交流,你的ddr3调试成功了吗?

你好,我最近也在弄ddr3,初始化的init_calib_complete信号仿真能拉高,下到板子上就一直为低,请问可能是啥问题。或者给个联系方式指导下表示不太懂

学习了

spartan6的mig核的信号跟v7的不一样,还是高端器件的好调

现在谁还在弄这方面的东西,一起交流下,我也在弄ddr3读写。504267997

今天我也碰到这个问题,直接用example design都不行,后来换了块板子好了。

你好 最近我也在调ddr3 可否加QQ交流下? 我的 1029470549 你也是NEU的?

我在写,想请教一下问题,刚开始学习看完帖子,收获很大啊

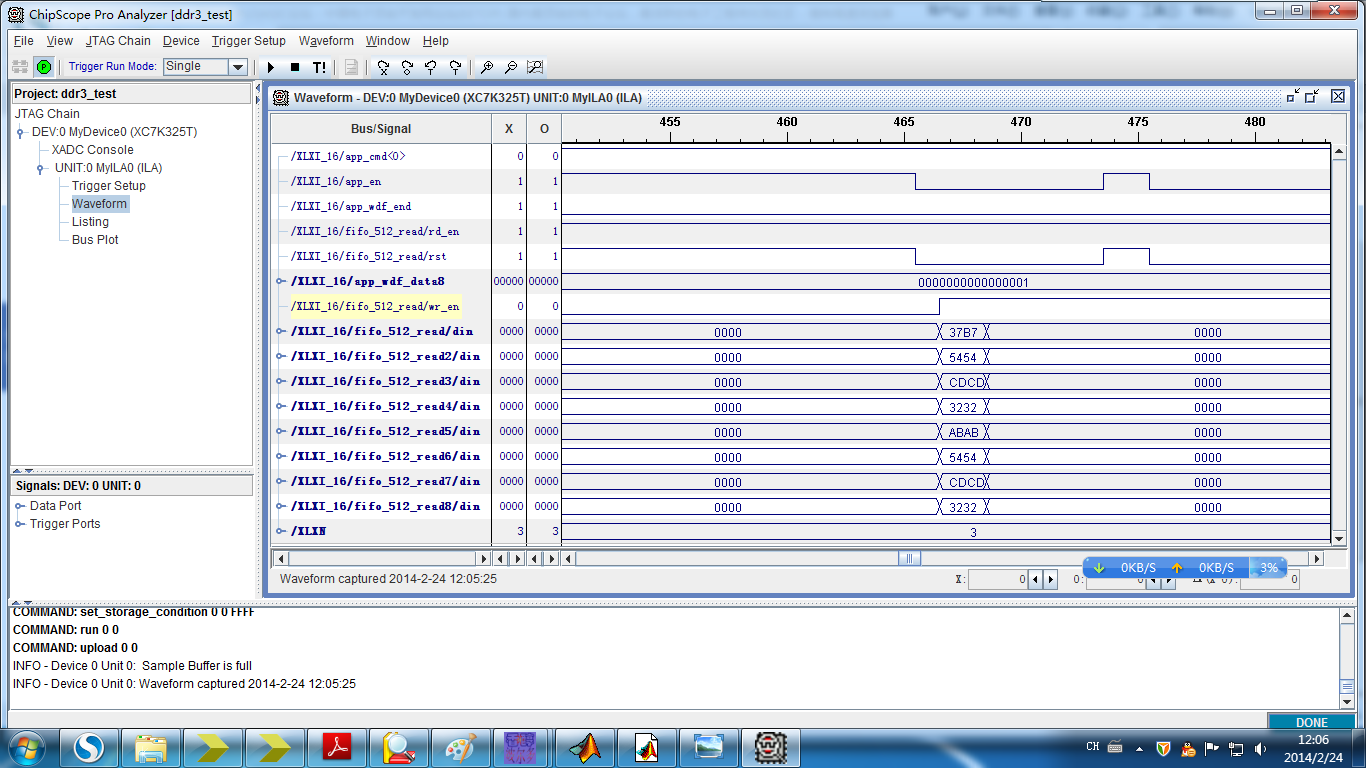

ddr3初始化的init_calib_complete信号仿真能拉高,下到板子上就一直为低,请问可能是啥问题。或者给个联系方式指导下没看图,可是发现你的读写的突发长度不一样,写是4,读是8

最近在学习调试ddr3,能否请教一下。最近也在调DDR读写,可以分享下调试代码吗?请问这个和MCB控制DDR读写有什么不同啊

仿真和板子根本就不是一回事,仿真初始化肯定会拉高,初始化不成功,应该是硬件的问题,先检查一下时钟有没有问题,然后器件啥的

init_calib_complete这个信号在新的MIG核中应该是phy_init_done吧!