请教综合时产生的时序报告分析

时间:10-02

整理:3721RD

点击:

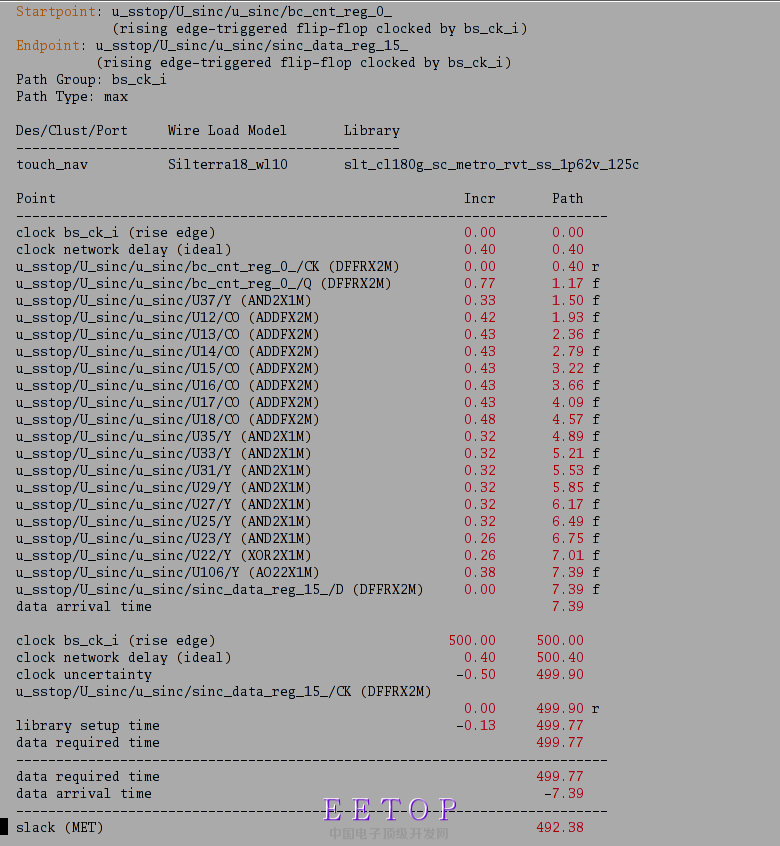

我对其中计算的路径延时有点不明白。根据setup time的要求,Tsetup<T-Tco-Tdelay+Tpd(其中T为时钟周期,Tco为D1->Q1的延时,Tdelay为Q1->D2的延时,Tpd是时钟延时),则有(T+Tpd-Tsetup)-(Tco+Tdelay)>0,实际路径所需的时间应该是Tco+Tdelay,为什么data arrivial time中还计算了时钟的延时?根据图中显示应该是(T+Tpd-Tsetup)-(Tpd+Tco+Tdelay).我有点不理解,请求帮助。

我对其中计算的路径延时有点不明白。根据setup time的要求,Tsetup<T-Tco-Tdelay+Tpd(其中T为时钟周期,Tco为D1->Q1的延时,Tdelay为Q1->D2的延时,Tpd是时钟延时),则有(T+Tpd-Tsetup)-(Tco+Tdelay)>0,实际路径所需的时间应该是Tco+Tdelay,为什么data arrivial time中还计算了时钟的延时?根据图中显示应该是(T+Tpd-Tsetup)-(Tpd+Tco+Tdelay).我有点不理解,请求帮助。

首先:

1): Tco:这个是CK1 -> Q1的延时。因为Q1是在CK1的沿变化的(rising or falling)。跟数据到D1没有关系(数据即使很早到了D1,没有CK1的沿,Q1同样不会变化)。

2): 你要明白clock skew。就是clock到CK1(clock pin of DFF1)跟CK2的时间的差异(就是你所说的Tpd1,Tpd2)。所以,公式应该是:

T-Tco1-Tdelay+(Tpd2 - Tpd1) > Tsetup2_req.

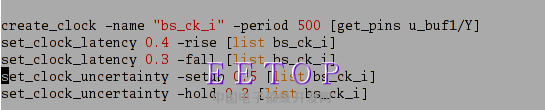

对setup分析很透彻,受教了。但是图片中的报告分析,clock network delay是指什么?是指你说的(Tpd1-Tpd2)么?

前面的是:Tpd1, 靠后的是Tpd2

但是我只设置了个时钟延时呀,难道是设置一个set_clock_lantency,就对所有就设置了?