关于DFI3.1使用dfi_wrdata_cs_n写操作的问题

时间:10-02

整理:3721RD

点击:

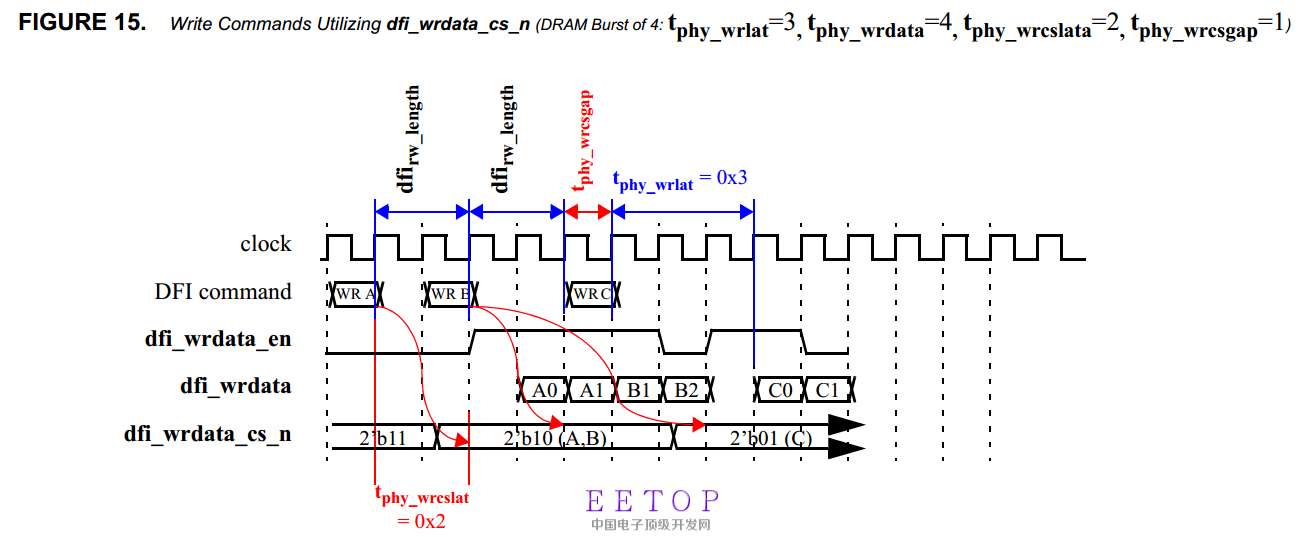

最近在学习DFI3.1的协议文档,在看到协议文档中使用dfi_wrdata_cs_n进行写操作的时候发现一点我无法理解的问题,如下图所示

从协议前文的描述来看写命令发出后,等待Tphy_wrcslat,dfi_wrdata_cs_n跳变为期望值,然后dfi_wrdata_cs_n至少要保持期望值的时间为DFIrw_length + Tphy_wrcsgap。

如上图所示,Tphy_wrcslat=2,DFIrw_length=2,Tphy_wrcsgap=1,那么WR A和WR B命令发出之后,等待2个时钟周期,dfi_wrdata_cs_n至少要保持3个时钟周期,对于WR A,dfi_wrdata_cs_n显然是满足要求的,但是从WR B来看dfi_wrdata_cs_n就不满足要求了。那么这个地方应该如何理解呢?