计数器为什么会出现这种突变跳转的情况?

时间:10-02

整理:3721RD

点击:

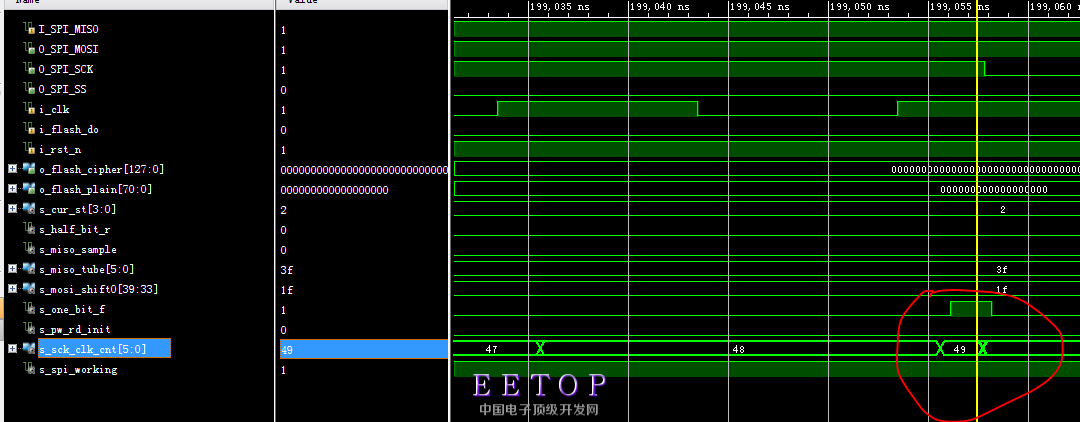

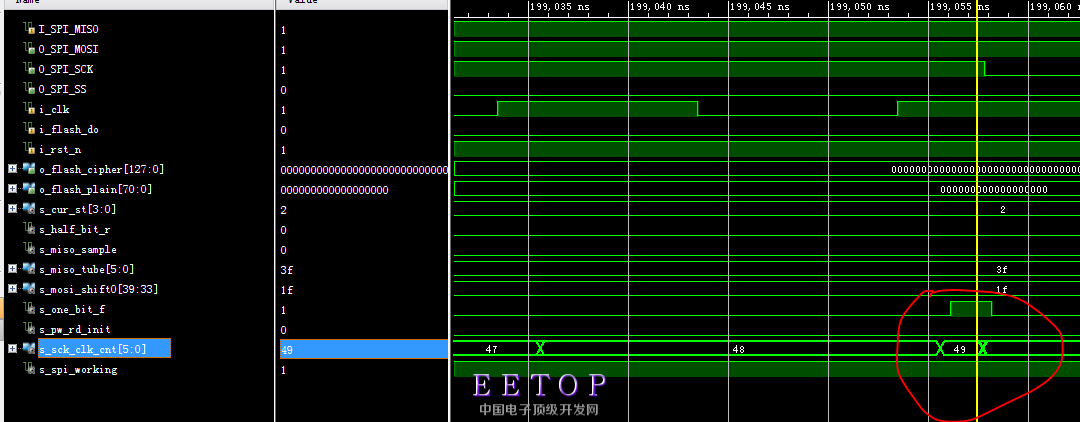

这个地方布线后的时序仿真为什么会出现这种突变的情况啊,在板子上测试抓信号时这里好像的确有跳变

计数器的SCK_div值是50 ,按理说计数器应该在49一个周期后,下个时钟来的时候才变为0啊,但是看起来提前跳变了

这有可能是什么情况造成的啊?

但是时序仿真就有突变,然后在板子上的确也没有抓到49的信号,应该是时序仿真的情况,跳过去了,没采样到

很奇怪为什么会这样

计数器的SCK_div值是50 ,按理说计数器应该在49一个周期后,下个时钟来的时候才变为0啊,但是看起来提前跳变了

这有可能是什么情况造成的啊?

功能仿真正确吗?

正常不过了,原因是各计数器输出到组合逻辑的延时不一样。

实现后的功能仿真都非常正常的:

但是时序仿真就有突变,然后在板子上的确也没有抓到49的信号,应该是时序仿真的情况,跳过去了,没采样到

很奇怪为什么会这样

但是我使用的是时序逻辑电路哇,理论上始终没来之前不应该变哇

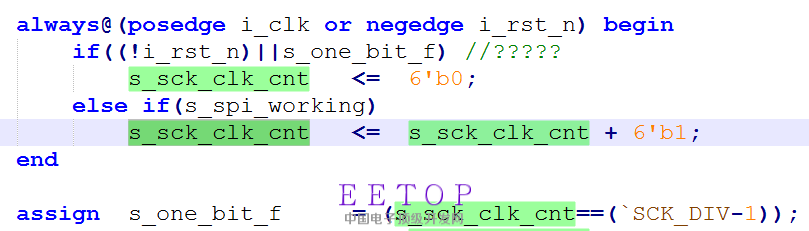

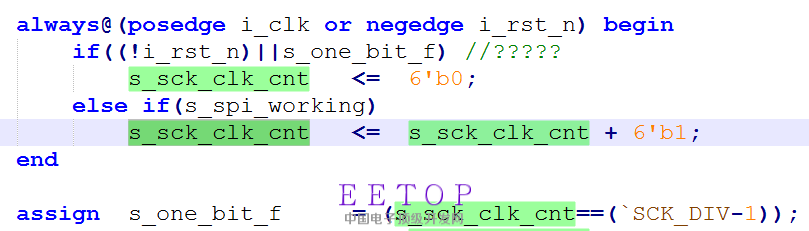

你试一下把 if((!i_rst_n)||s_one_bit_f) 条件拆开!初步怀疑是综合工具把你的s_one_bit_f信号综合成复位端了,你可以改后试一下,也可以直接看网表确定!

好像真的是耶!拆开就好啦!太感谢啦!

顺带问一下怎么样查看网标哇?是看那个综合出来的逻辑原理图么?

嗯,一般来说综合后的组合逻辑可能不能一眼看出,但配合仿真还是能看出的。以后出这种问题你可以从出错的寄存器往回推,比如触发器的输入信号有哪些异常!虽然有点痛苦!

非常感谢!