写的一个24s倒计时,怎么输出总不对,求解答

时间:10-02

整理:3721RD

点击:

顶层:module digital(timerh,timerl,over,reset,stop,clk );

output [6:0] timerh;

output [6:0] timerl;

output over;

input stop;

input reset;

input clk;

wire [1:0]H;

wire [3:0]L;

wire clk_1;

fenpin uut1(clk,clk_1);

basketballtimer uut2(over,H,L,reset,stop,clk_1);

cd4511 uut3(timerh[6:0],{2'b00,H[1:0]});

cd4511 uut4(timerl[6:0],L[3:0]);

endmodule

分频:module fenpin(clk,clk_1

);

input clk;

output clk_1;

reg [1:0] cnt;

reg clk_1;

always @(posedge clk)

begin

if(cnt==2'b1_1001_0000_0000_0000_0000)

begin

clk_1<=~clk_1;

cnt<=0;

end

else

cnt<=cnt+1;

end

endmodule

计时:module basketballtimer(over,H,L,reset,stop,clk_1

);

output over;

output [1:0]H;

output [3:0]L;

input reset;

input stop;

input clk_1;

reg [4:0]Q;

assign over=(Q==5'd0);

assign H=Q/10;

assign L=Q%10;

always@(posedge clk_1 or negedge reset or negedge stop)

begin

if(~reset)

Q<=5'd23;

else

begin

if(~stop)

Q<=Q;

else

begin

if(Q>5'd0)

Q<=Q-1'b1;

else

Q<=Q;

end

end

end

endmodule

显示:

module cd4511(Y,A

);

output reg [6:0]Y;

input [3:0]A;

always @(*)

begin

case(A)

4'd0:Y<=7'b1000_000;

4'd1:Y<=7'b1111_001;

4'd2:Y<=7'b0100_100;

4'd3:Y<=7'b0110_000;

4'd4:Y<=7'b0011_001;

4'd5:Y<=7'b0010_010;

4'd6:Y<=7'b0000_010;

4'd7:Y<=7'b1111_000;

4'd8:Y<=7'b0000_000;

4'd9:Y<=7'b0010_000;

default:Y<=7'b1000_000;

endcase

end

endmodule

testbench:

module tgghh;

// Inputs

reg reset;

reg stop;

reg clk;

// Outputs

wire [6:0] timerh;

wire [6:0] timerl;

wire over;

// Instantiate the Unit Under Test (UUT)

digital uut (

.timerh(timerh),

.timerl(timerl),

.over(over),

.reset(reset),

.stop(stop),

.clk(clk)

);

initial begin

clk=0;

reset=1;

stop=1;

#10 reset=0;

#20 reset=1;

#200 stop=0;

#50 stop=1;

@(posedge over);

#20 $stop;

end

always #5 clk=~clk;

endmodule

output [6:0] timerh;

output [6:0] timerl;

output over;

input stop;

input reset;

input clk;

wire [1:0]H;

wire [3:0]L;

wire clk_1;

fenpin uut1(clk,clk_1);

basketballtimer uut2(over,H,L,reset,stop,clk_1);

cd4511 uut3(timerh[6:0],{2'b00,H[1:0]});

cd4511 uut4(timerl[6:0],L[3:0]);

endmodule

分频:module fenpin(clk,clk_1

);

input clk;

output clk_1;

reg [1:0] cnt;

reg clk_1;

always @(posedge clk)

begin

if(cnt==2'b1_1001_0000_0000_0000_0000)

begin

clk_1<=~clk_1;

cnt<=0;

end

else

cnt<=cnt+1;

end

endmodule

计时:module basketballtimer(over,H,L,reset,stop,clk_1

);

output over;

output [1:0]H;

output [3:0]L;

input reset;

input stop;

input clk_1;

reg [4:0]Q;

assign over=(Q==5'd0);

assign H=Q/10;

assign L=Q%10;

always@(posedge clk_1 or negedge reset or negedge stop)

begin

if(~reset)

Q<=5'd23;

else

begin

if(~stop)

Q<=Q;

else

begin

if(Q>5'd0)

Q<=Q-1'b1;

else

Q<=Q;

end

end

end

endmodule

显示:

module cd4511(Y,A

);

output reg [6:0]Y;

input [3:0]A;

always @(*)

begin

case(A)

4'd0:Y<=7'b1000_000;

4'd1:Y<=7'b1111_001;

4'd2:Y<=7'b0100_100;

4'd3:Y<=7'b0110_000;

4'd4:Y<=7'b0011_001;

4'd5:Y<=7'b0010_010;

4'd6:Y<=7'b0000_010;

4'd7:Y<=7'b1111_000;

4'd8:Y<=7'b0000_000;

4'd9:Y<=7'b0010_000;

default:Y<=7'b1000_000;

endcase

end

endmodule

testbench:

module tgghh;

// Inputs

reg reset;

reg stop;

reg clk;

// Outputs

wire [6:0] timerh;

wire [6:0] timerl;

wire over;

// Instantiate the Unit Under Test (UUT)

digital uut (

.timerh(timerh),

.timerl(timerl),

.over(over),

.reset(reset),

.stop(stop),

.clk(clk)

);

initial begin

clk=0;

reset=1;

stop=1;

#10 reset=0;

#20 reset=1;

#200 stop=0;

#50 stop=1;

@(posedge over);

#20 $stop;

end

always #5 clk=~clk;

endmodule

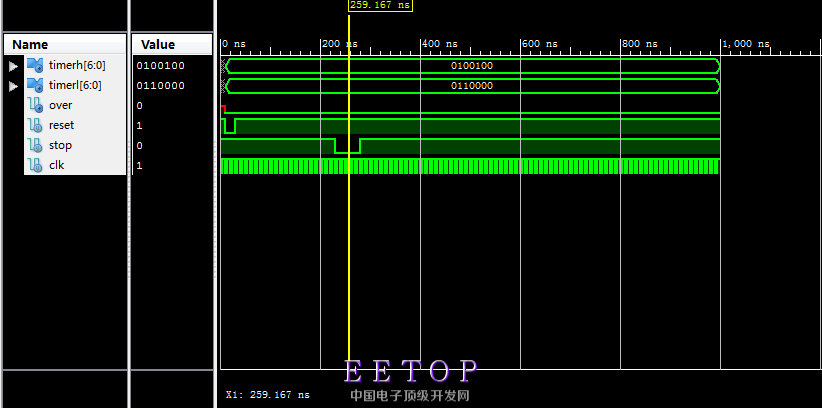

它的仿真图像输出一直是23

懂了,我的那个分频的不对,在仿真时不应该这样,实际中才应该那样写

分频的计数器位宽都不匹配啊!

那个是我修改了之后,没改回来,之前是reg [24:0] 也是不对的

学习了