Xilinx FIFO ip核调用

时间:10-02

整理:3721RD

点击:

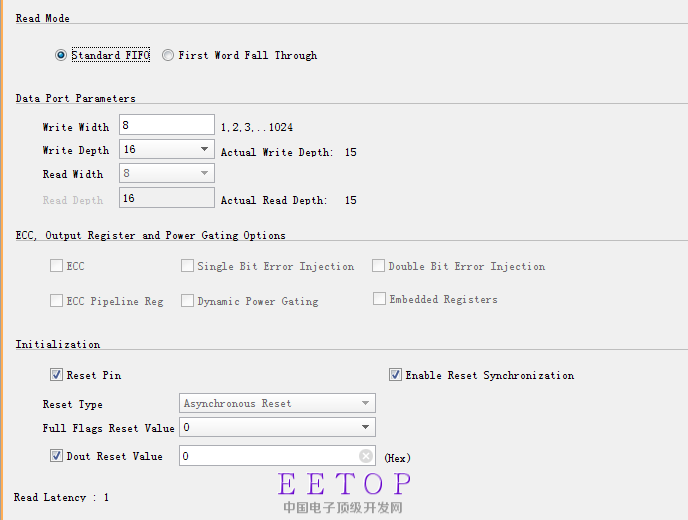

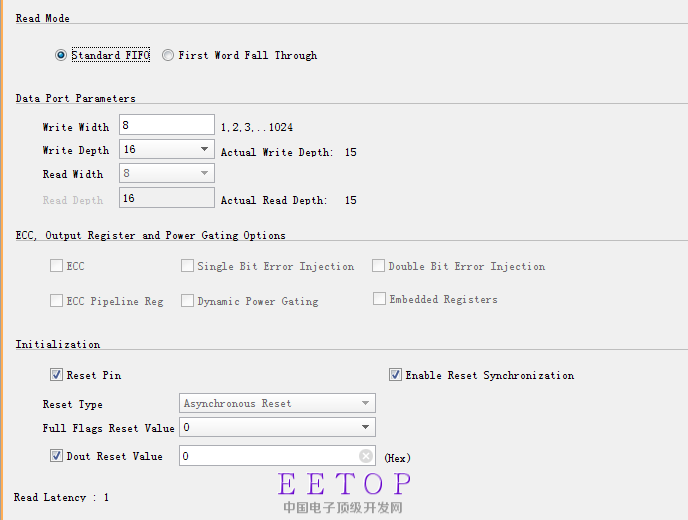

在vivado2015中调用fifo ip核,异步的,写时钟100M,读时钟50M;具体配置如下:

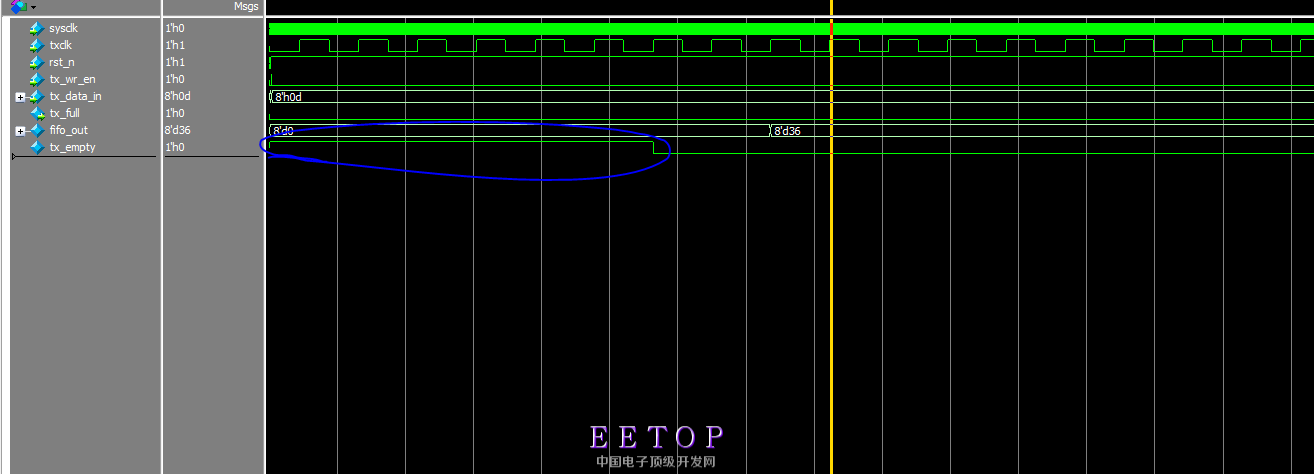

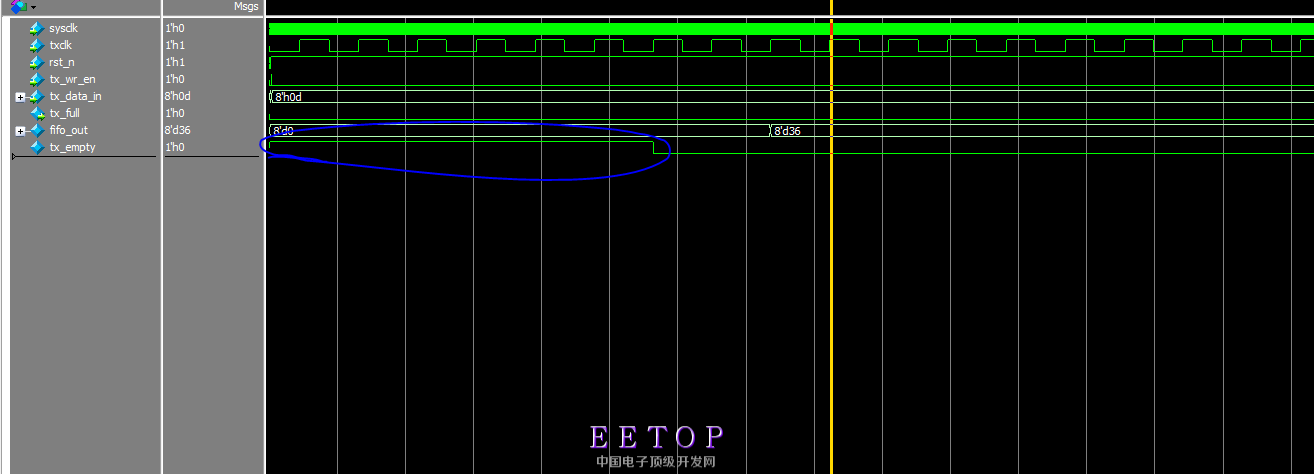

复位是高电平复位,但发现数据能够写进去,也能够读出来,但是就是empty信号出现问题,理应只要有一个数据写入fifo,那么empty信号也会相应的拉低,但发现empty要在数据写完之后才变成低电平,如下图所示:

其中,sysclk是写时钟,txclk是读时钟,tx_wr_en是写使能,tx_data_in是写入的数据,tx_empty是fifo空信号,为什么数据已经写进入了,要等六七个读时钟后,空信号才会拉低呢?而数据明明早就写入fifo了。谢谢了!

复位是高电平复位,但发现数据能够写进去,也能够读出来,但是就是empty信号出现问题,理应只要有一个数据写入fifo,那么empty信号也会相应的拉低,但发现empty要在数据写完之后才变成低电平,如下图所示:

其中,sysclk是写时钟,txclk是读时钟,tx_wr_en是写使能,tx_data_in是写入的数据,tx_empty是fifo空信号,为什么数据已经写进入了,要等六七个读时钟后,空信号才会拉低呢?而数据明明早就写入fifo了。谢谢了!

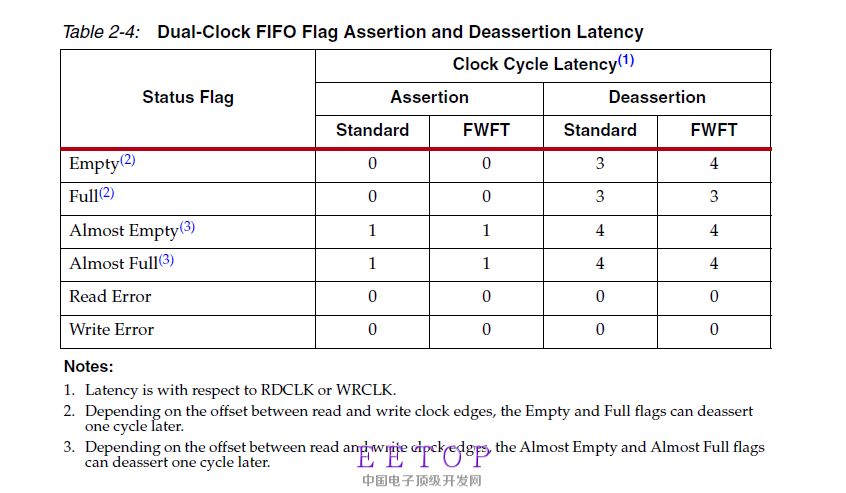

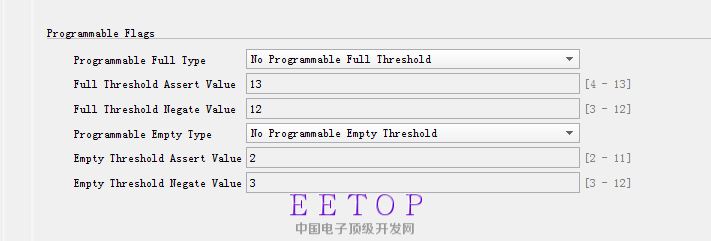

你可以看看fifo的UG上面对empty和full信号的描述。手册中说到:满空信号可以0延迟置高,但是清零的话会有延迟,延迟多久可以在生成fifo ip的时候设置。

貌似vivado的ip generator里面没有这样的配置吧!

好的,我尝试下,谢谢了!

貌似不行,里面的值有范围

我不知道怎么发图片。在fifo generator的第一个basic页面当中,如果你时钟设置为independent clocks block ram 的话下面会有个synchronization stages,这个好像叫同步等级吧,可能跟这个设置的有关,你可以尝试一下。

你看看这个