各位帮看一下这个PWM实现程序问题出在哪里了,调试半天了没弄出来,谢谢

这是原代码:

module pwm(clk,clk5s,duty,pwmout);

reg [7:0]countout;

input clk,clk5s;

input [7:0]duty;

output pwmout;

always@(posedge clk )

if (clk5s) countout <= 8'd0;

else countout <= countout+1;

assign pwmout=(countout<duty)?1'b1:1'b0;

endmodule

这是testbench:

module pwm_test;

reg clk;

reg[7:0]duty;

reg [31:0]count;

reg clk5s;

wire pwm;

initial

begin

clk=0;

duty=8'd10;

count = 32'd0;

clk5s=0;

end

always#1 clk=~clk;

pwm pl(.clk(clk),.clk5s(clk5s),.duty(duty),.pwmout(pwm));

endmodule

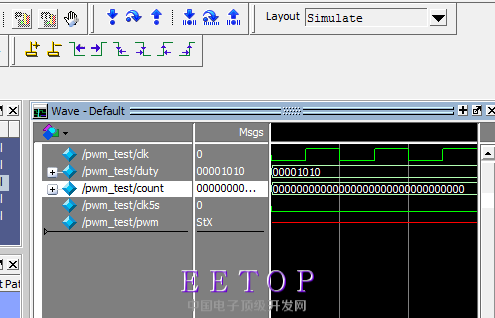

用modelsim仿真出来的信号如下

这个不正确啊,本人新手,望各位指点一下,非常感谢

不要,不要沉。

你的代码风格太差了,修改一下吧,而且count位数都不对

仿真时间够吗

countout 没有初始态!

本应该clk5s的1'b1同步复位,但你将其tie成0了,countout一直没被复位,

在此基础上+1,不定态,

进一步导致pwmout不定态。

两个办法:1)初始化countout;2)clk5s中间产生高电平;

楼上正解。countout没初始值,想当然的认为是00,实际上是xx,xx+1是多少?还是xx!所以,要么初始化countout,要么给个条件让它步入正轨

Try see see ! ^^

Modify testbench :

------------------------------------

module pwm_test;

reg clk;

reg[7:0]duty;

reg [31:0]count;

reg clk5s;

wire pwm;

initial

begin

clk=0;

duty=8'd10;

count = 32'd0;

clk5s=1'b1;

#10;

clk5s=1'b0;

end

always#1 clk=~clk;

pwm pl(.clk(clk),.clk5s(clk5s),.duty(duty),.pwmout(pwm));

endmodule

Try see see ! ^^

Modify testbench :

------------------------------------

module pwm_test;

reg clk;

reg[7:0]duty;

reg [31:0]count;

reg clk5s;

wire pwm;

initial

begin

clk=0;

duty=8'd10;

count = 32'd0;

clk5s=1'b1;

#10;

clk5s=1'b0;

end

always#1 clk=~clk;

pwm pl(.clk(clk),.clk5s(clk5s),.duty(duty),.pwmout(pwm));

endmodule