请教PCIE的时序问题

时间:10-02

整理:3721RD

点击:

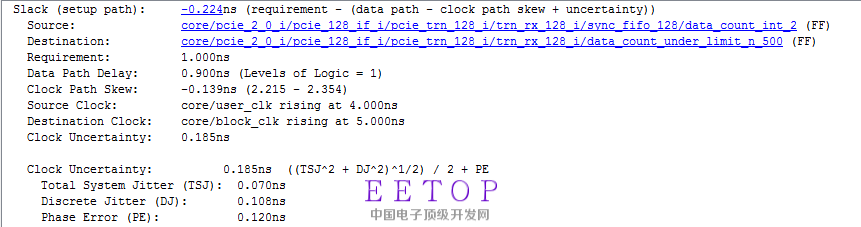

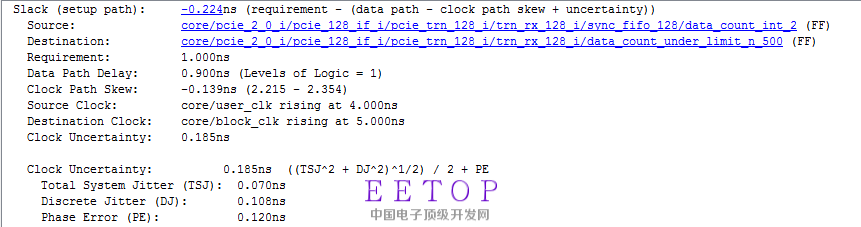

小弟新手,最近在根据xilinx的xapp1052弄pcie,做gen2 8x时在时序上遇到点问题,请问各位图中这种情况该怎么处理

其中user_clk 250MHz,block_clk 500MHz,是同一个MMCM出来的两个时钟

由于是core那边的,我搞得不太清楚不敢动,还请各位大神不吝赐教!

我的理解Requirement那一项的时间应该是时钟的周期,就算按500MHz的时钟来算也应该是2ns,为什么实际是1ns呢?

另外各位有碰到过使用ChipScope抓信号时,在确定触发事件发生的情况下,ChipScope却没抓到的情况吗?

其中user_clk 250MHz,block_clk 500MHz,是同一个MMCM出来的两个时钟

由于是core那边的,我搞得不太清楚不敢动,还请各位大神不吝赐教!

我的理解Requirement那一项的时间应该是时钟的周期,就算按500MHz的时钟来算也应该是2ns,为什么实际是1ns呢?

另外各位有碰到过使用ChipScope抓信号时,在确定触发事件发生的情况下,ChipScope却没抓到的情况吗?

ChipScope抓不到数据,有时候可能是ChipScope采样时钟不够原因

这是两个异步时钟,工具在分析最坏的情形,1ns

谢谢,不过我的采样时钟就是被采样接口的同步时钟,还有什么其他的原因吗?

谢谢。可以讲一下处理这种情况的基本思路吗?

设false path