在FPGA内部生成RAM,在modelsin下仿真数据正确,但是下载到板子上数据出错?

时间:10-02

整理:3721RD

点击:

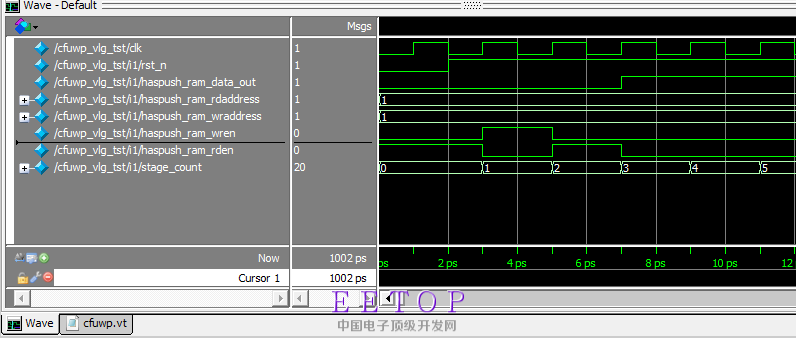

在FPGA内部生成RAM大小为256*1,初始化mif文件全是0,现在对地址1先进行读,接着将数据1写进地址1,接着再对地址1读,按道理应该先读出0,写了之后在读出1,在modelsin下仿真ram输出数据正确,但是下载到板子上数据出错?主要是haspush_ram_data_out信号,应该是先低后高,但是抓出来全是高电平!

程序如下:

//////////////////////////////////////////////////////////////////////////////////

module cfuwp(

input clk,

input

rst_n,

output haspush_ram_data_out

);

wire [7:0]haspush_ram_rdaddress,haspush_ram_wraddress;

wire haspush_ram_wren,haspush_ram_rden;

wire clk_200M;

reg [4:0]stage_count;

assign haspush_ram_wren=(stage_count==5'd1)?1'b1:1'b0;//写

assign haspush_ram_rden=(stage_count==5'd0 | stage_count==5'd2)?1'b1:1'b0;//两次读

assign haspush_ram_rdaddress=8'd1;

assign haspush_ram_wraddress=8'd1;

always @(posedge clk or negedge rst_n)

if(!rst_n)

stage_count<=5'b0;

else

stage_count<=stage_count+1'b1;

pll_200 pll_200_m0(.inclk0(clk),.c0(clk_200M));//又50Mhz时钟倍频到200Mhz用于生成下载到板子上的采样时钟

haspush_ram m3(.clock(clk),.data(1'b1),.rdaddress(haspush_ram_rdaddress),.rden(haspush_ram_rden),.wraddress(haspush_ram_wraddress),.wren(haspush_ram_wren),.q(haspush_ram_data_out));

endmodule

建议用FPGA内部的软逻辑分析 ChipScope或者signaltap 直接抓RAM接口再定位什么原因

rst 好怪 ..

always @(posedge clk or negedge rst_n)

但看 simulation rst 一直 low -> hi ..跟本沒有 negedge

去 reset 內部吧 .

请先判断时序是否满足啊?

第一张图就是用sigaltap抓的

是看输入时钟吗?

感觉逻辑没有问题,可能是复位问题吧,你先写10个地址,再从这10个地址读出来试试。