16bit处理器与32位SRAM的异步接口设计

时间:10-02

整理:3721RD

点击:

FPGA新手求教一下基本设计思路:

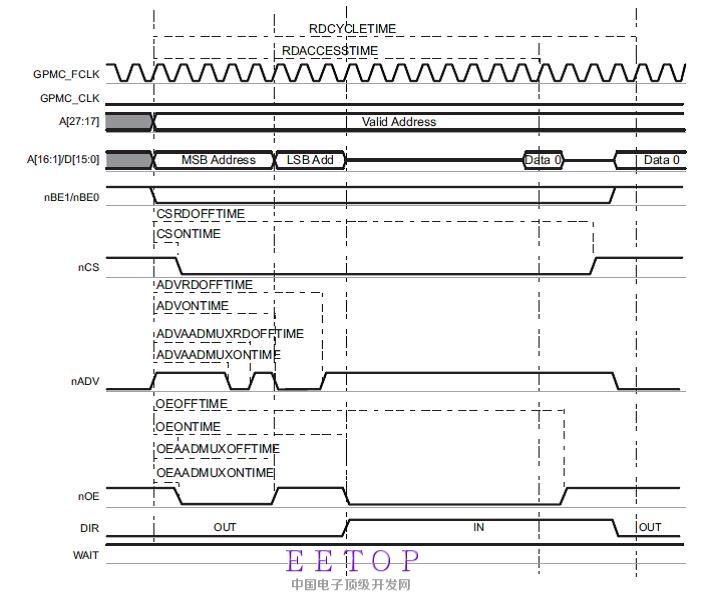

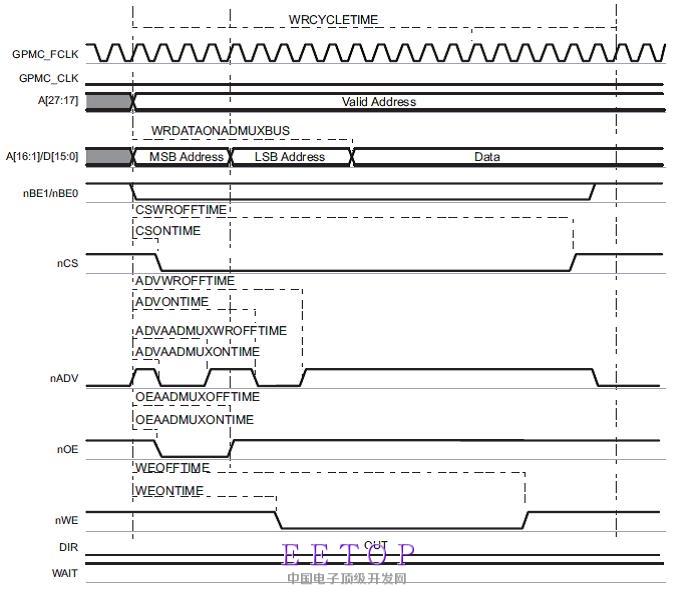

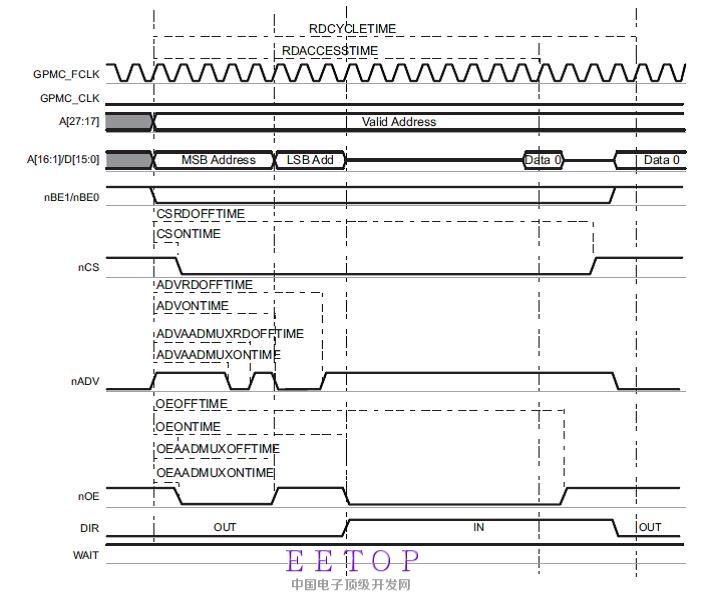

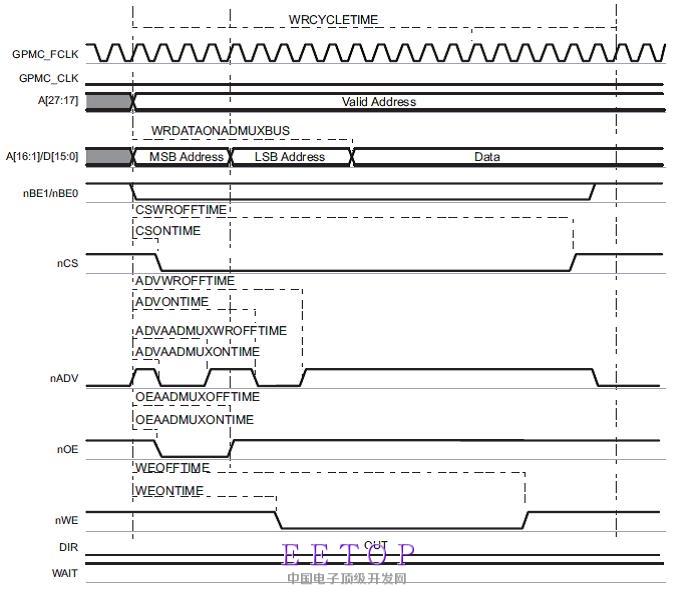

目前我需要用FPGA设计一个16bit处理器和32位SRAM的异步接口。 处理器是TI的AM3356,它的GPMC接口使用了AAD模式,地址和数据服用在1组总线上,这个总线的内部时钟是100M的。读写时序如下图所示:

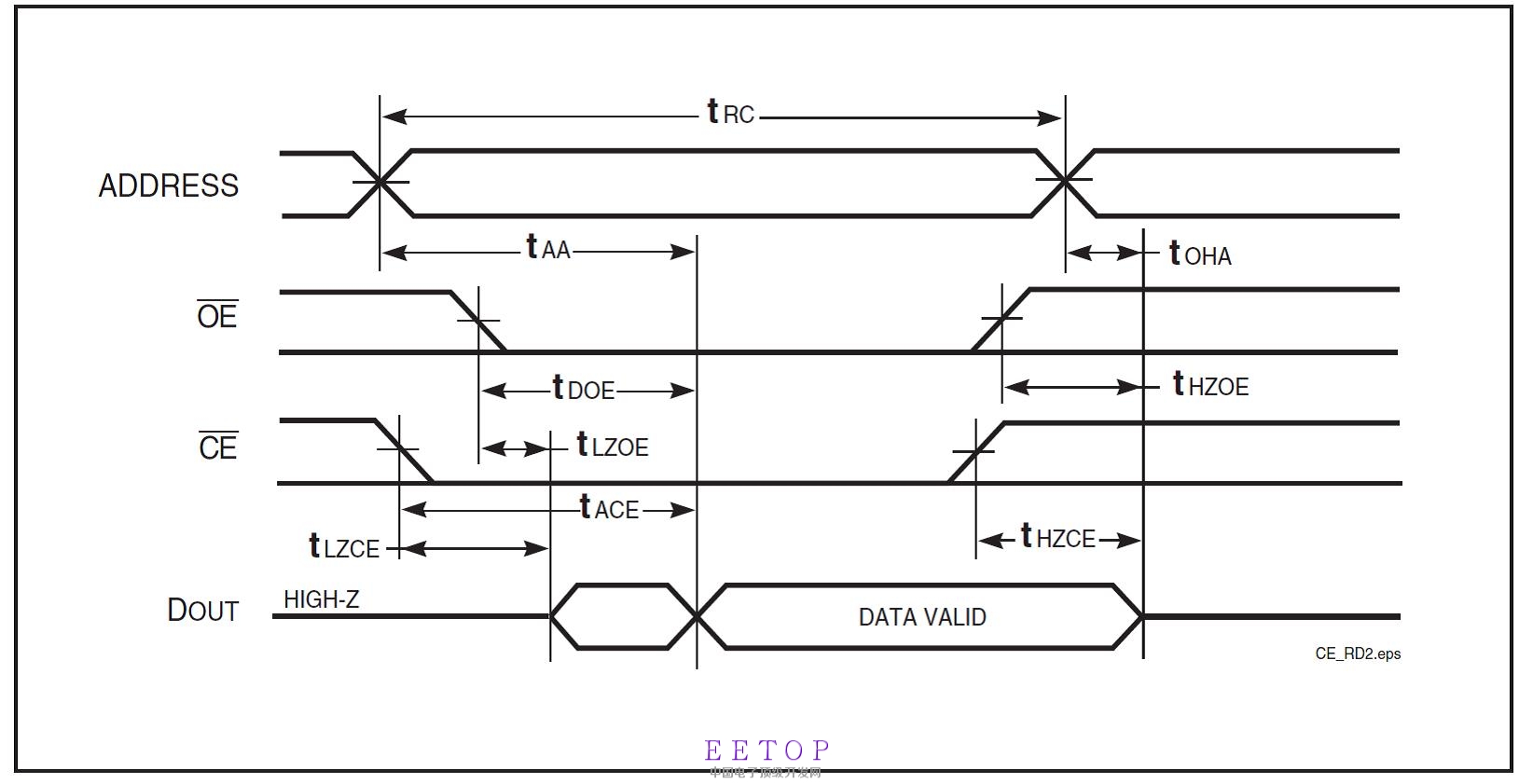

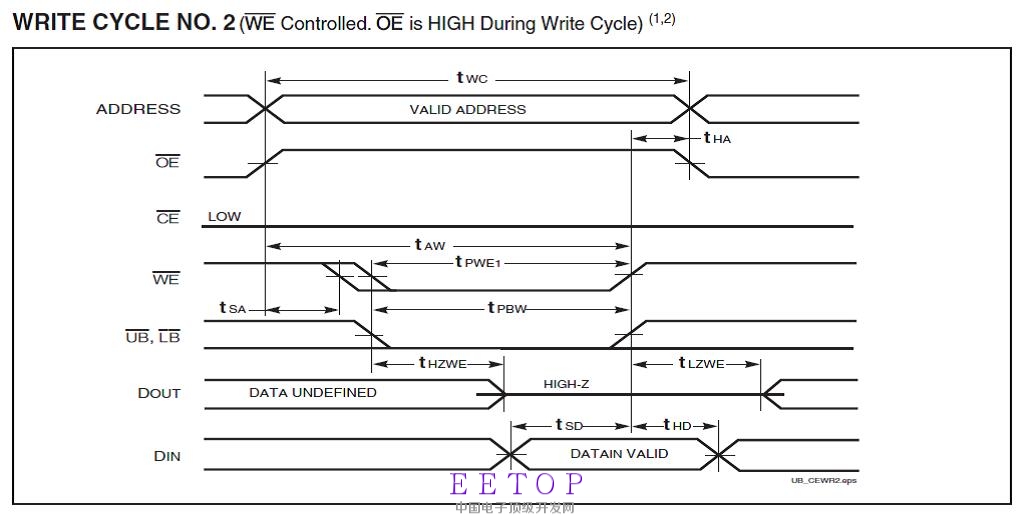

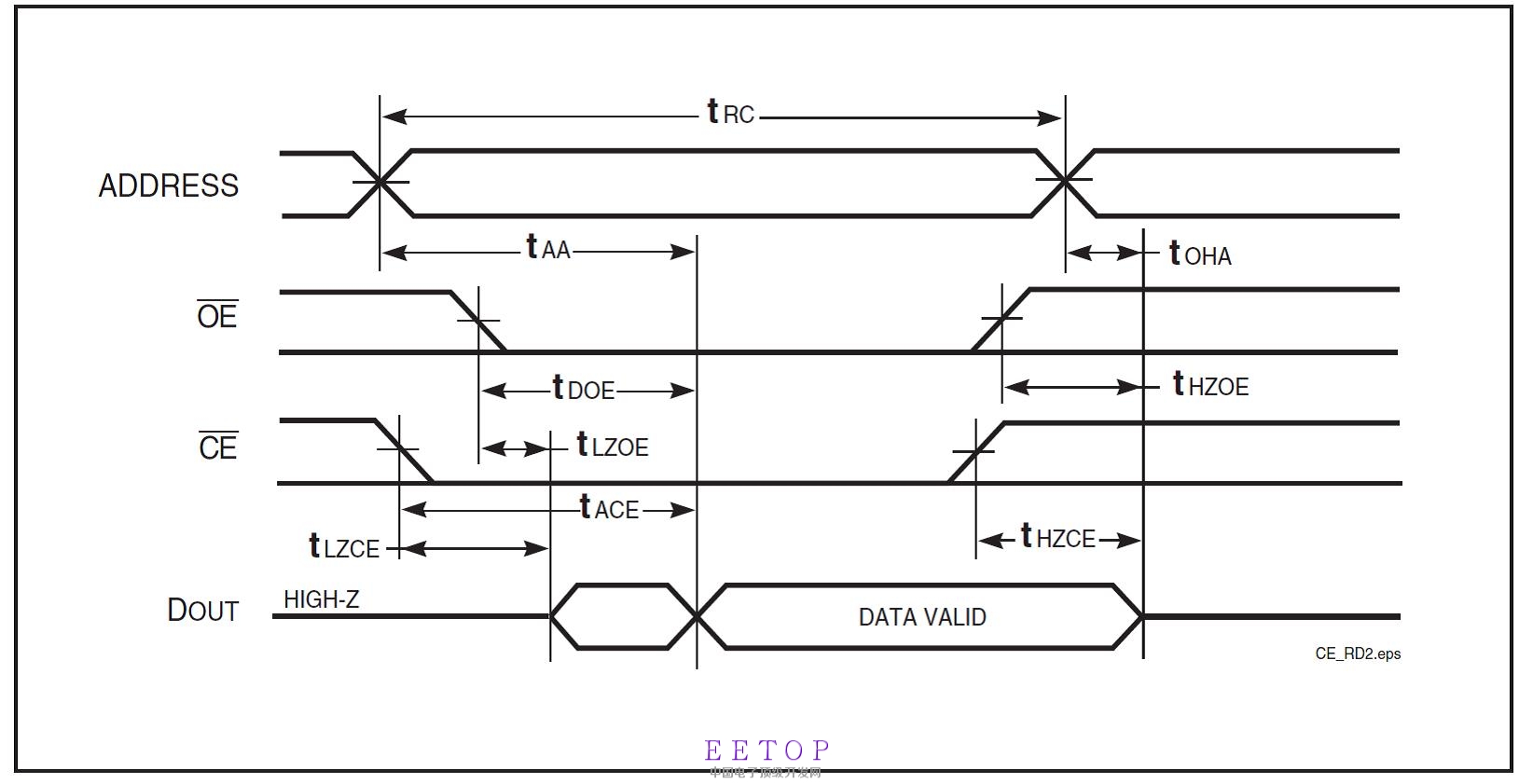

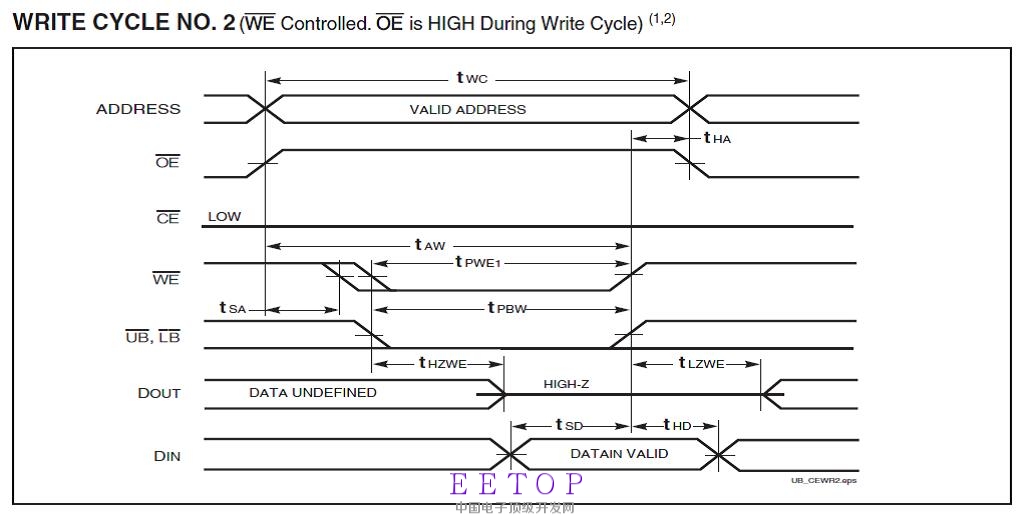

SRAM的读写时序就是比较普通的异步接口时序:

我的问题是

1.在FPGA中我需要用多快的时钟来采样信号。

2.我准备使用一个有限状态机先将AAD复用的总线分解为单独的地址和数据,然后再根据A1的值来确定处理器想要访问数据的高16位还是低16位,FPGA将使用SRAM的NBS信号mask不需访问的那16位数据,将FPGA内部的16位数据线连到需要访问的16位SRAM数据线上。请问这个方案是否可行,是否有风险?

3.我自己模拟了一个读的时序图:

有同事建议我在FPGA中设计一个FIFO,请问我上面的方案可行的话是否还需要FIFO?为什么?

多谢回答的大虾先!

目前我需要用FPGA设计一个16bit处理器和32位SRAM的异步接口。 处理器是TI的AM3356,它的GPMC接口使用了AAD模式,地址和数据服用在1组总线上,这个总线的内部时钟是100M的。读写时序如下图所示:

SRAM的读写时序就是比较普通的异步接口时序:

我的问题是

1.在FPGA中我需要用多快的时钟来采样信号。

2.我准备使用一个有限状态机先将AAD复用的总线分解为单独的地址和数据,然后再根据A1的值来确定处理器想要访问数据的高16位还是低16位,FPGA将使用SRAM的NBS信号mask不需访问的那16位数据,将FPGA内部的16位数据线连到需要访问的16位SRAM数据线上。请问这个方案是否可行,是否有风险?

3.我自己模拟了一个读的时序图:

有同事建议我在FPGA中设计一个FIFO,请问我上面的方案可行的话是否还需要FIFO?为什么?

多谢回答的大虾先!