MIG核数据错位的问题

时间:10-02

整理:3721RD

点击:

自己写了一个MIG的使用程序,大概就是写64个数,然后再全部读出来。

sysclk 100M refclk200 M

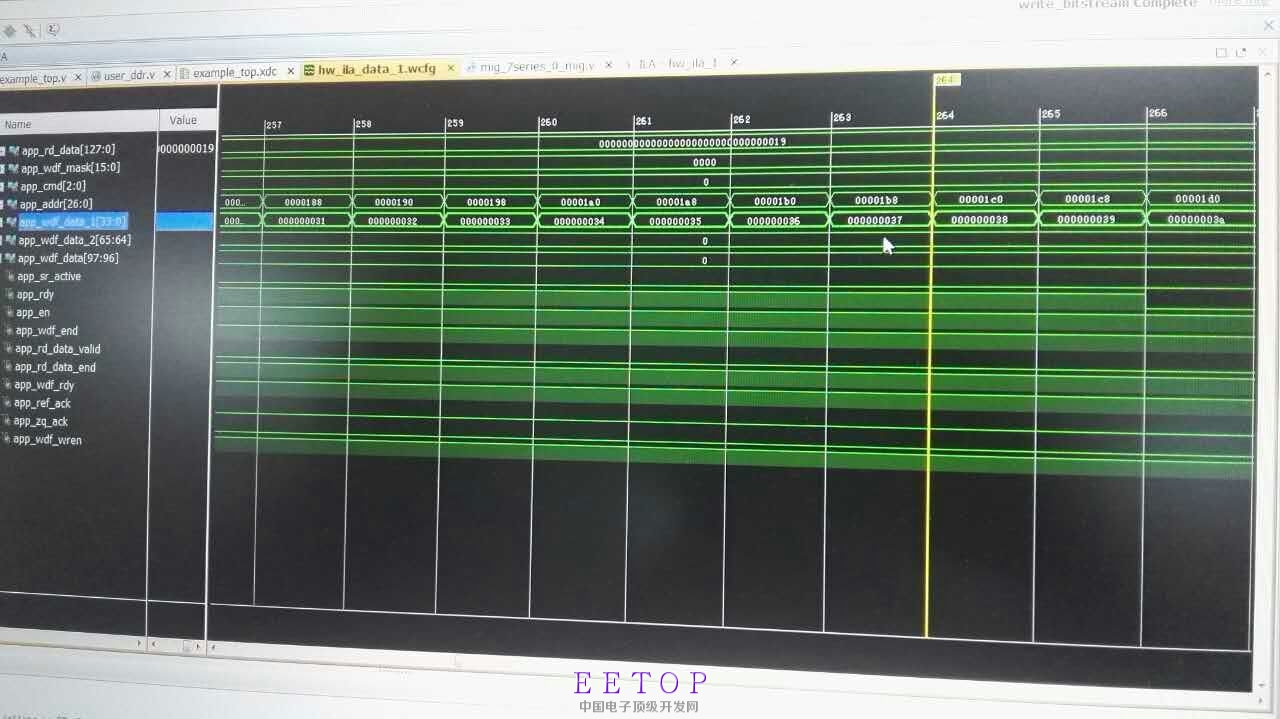

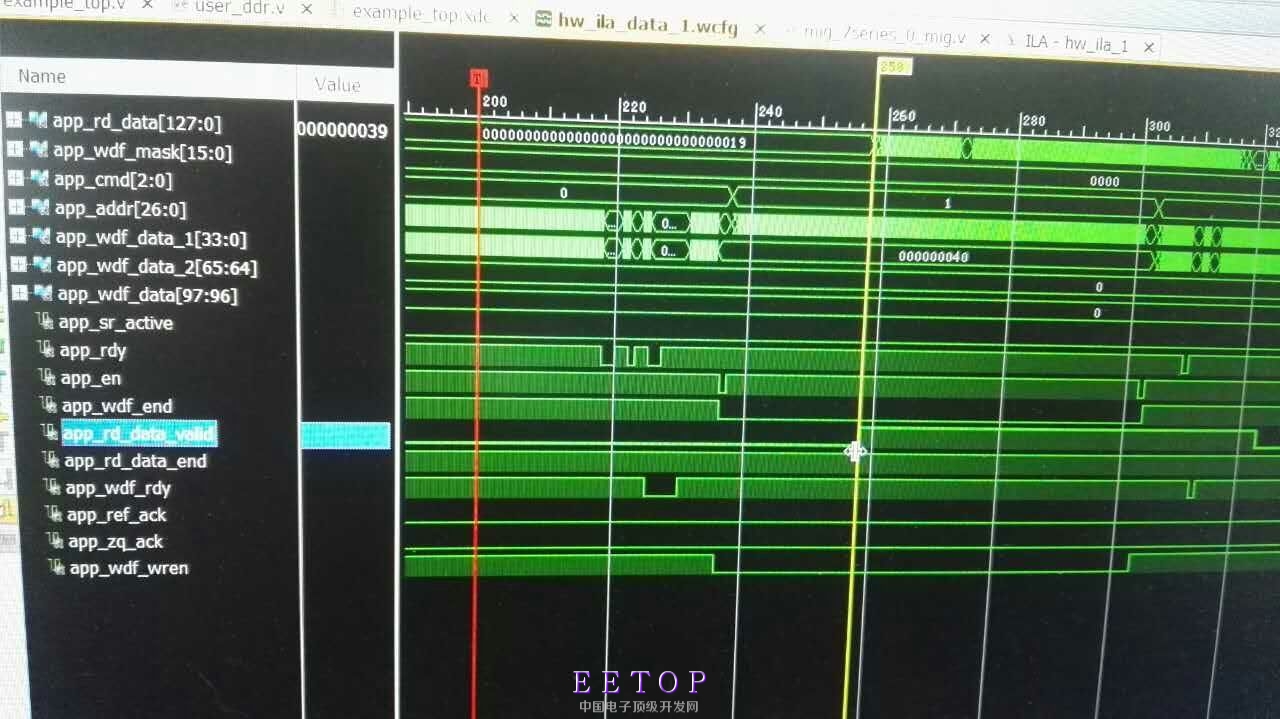

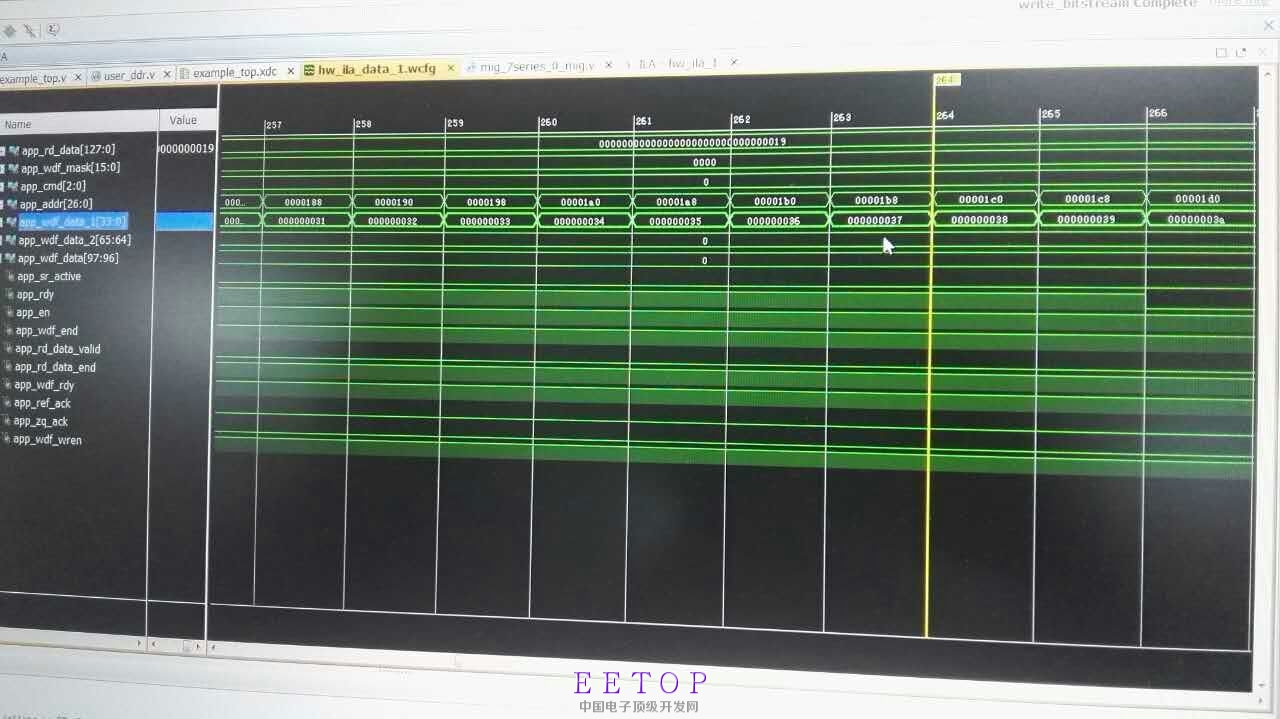

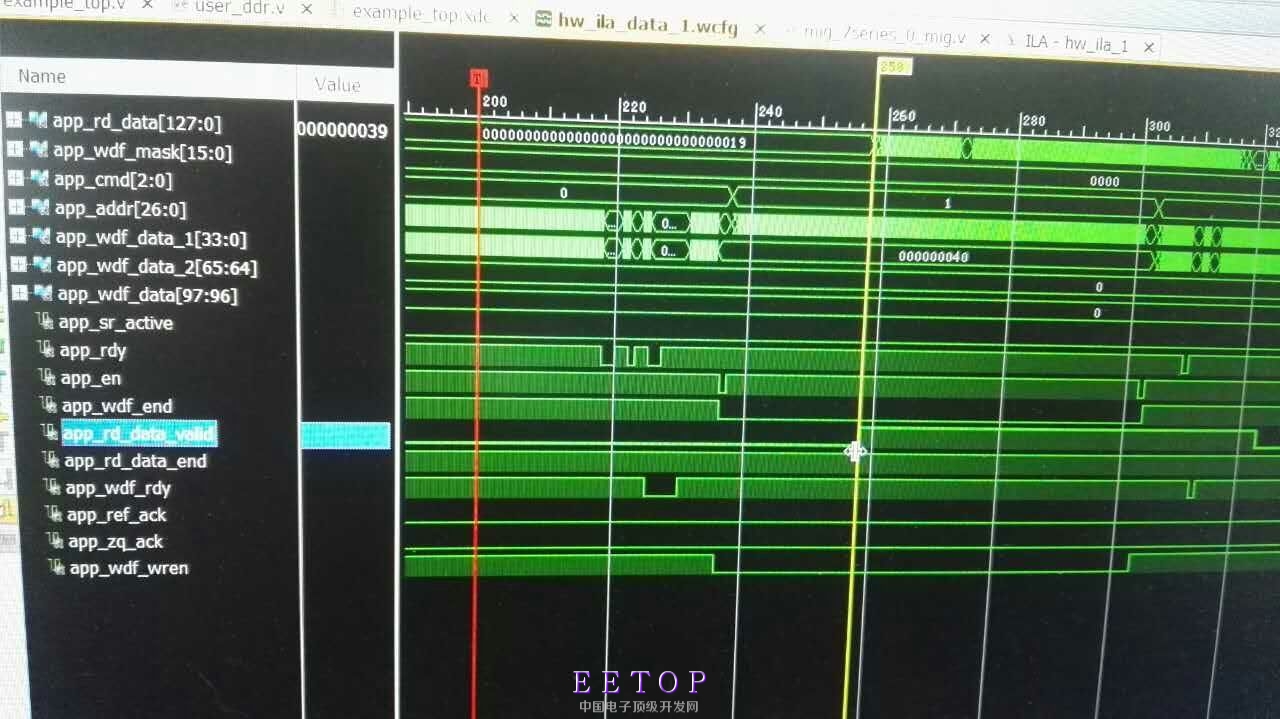

然后下载到板子上出了一些问题,如图所示。

问题主要有两个

1.读数据为1,写数据为0。可以看到当读数据的时候,rd_valid比开始读数据的点慢了非常多的周期。估计有20个周期。也就是利用app_cmd发出读信号后,过了大约20个周期,rd_valid才拉高。

2.我在写入的时候,数据从0开始每次加1,地址从0每次加8。但是读数据的时候,当rd_valid拉高后,第一个读出的数据是hex38。就算是读数据有延时,但是开始读hex38就很奇怪了。然后当数据读到64以后,又变为0从新开始。感觉就是数据错位了。但我并不能理解在哪里开始错位的。

望大神指教。

sysclk 100M refclk200 M

然后下载到板子上出了一些问题,如图所示。

问题主要有两个

1.读数据为1,写数据为0。可以看到当读数据的时候,rd_valid比开始读数据的点慢了非常多的周期。估计有20个周期。也就是利用app_cmd发出读信号后,过了大约20个周期,rd_valid才拉高。

2.我在写入的时候,数据从0开始每次加1,地址从0每次加8。但是读数据的时候,当rd_valid拉高后,第一个读出的数据是hex38。就算是读数据有延时,但是开始读hex38就很奇怪了。然后当数据读到64以后,又变为0从新开始。感觉就是数据错位了。但我并不能理解在哪里开始错位的。

望大神指教。