一个DDR3初始化失败的问题

自己定一个,因为是第一次调试ddr3,也不知道该怎么调试

有人帮帮我吗?告诉我下一步该怎么调试就行

自己顶一下,别沉了

没有调试过altera的,不过xilinx的有error提示,提示是哪一步出错了,你看看

ddr3的芯片手册你得研读明白才能设置

另外altera有uniphy ddr3的ip参数的很简单的介绍视频和详细的pdf

好好看看手册,初始化的问题会解决的

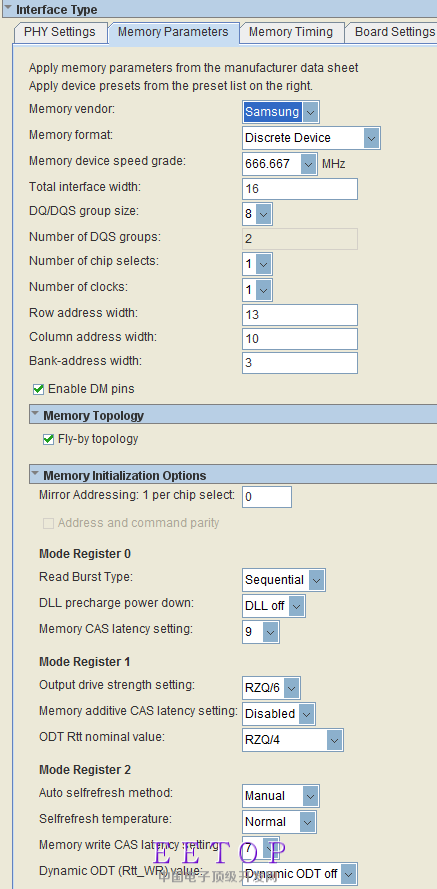

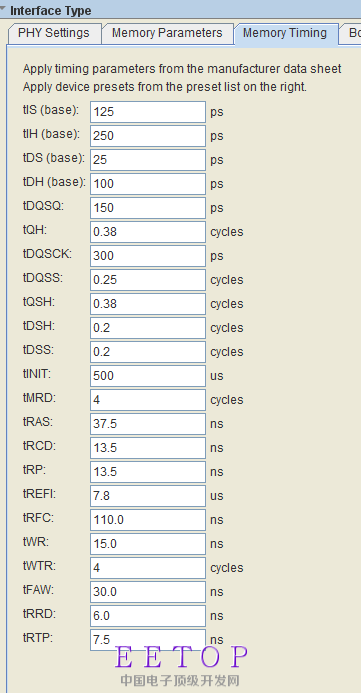

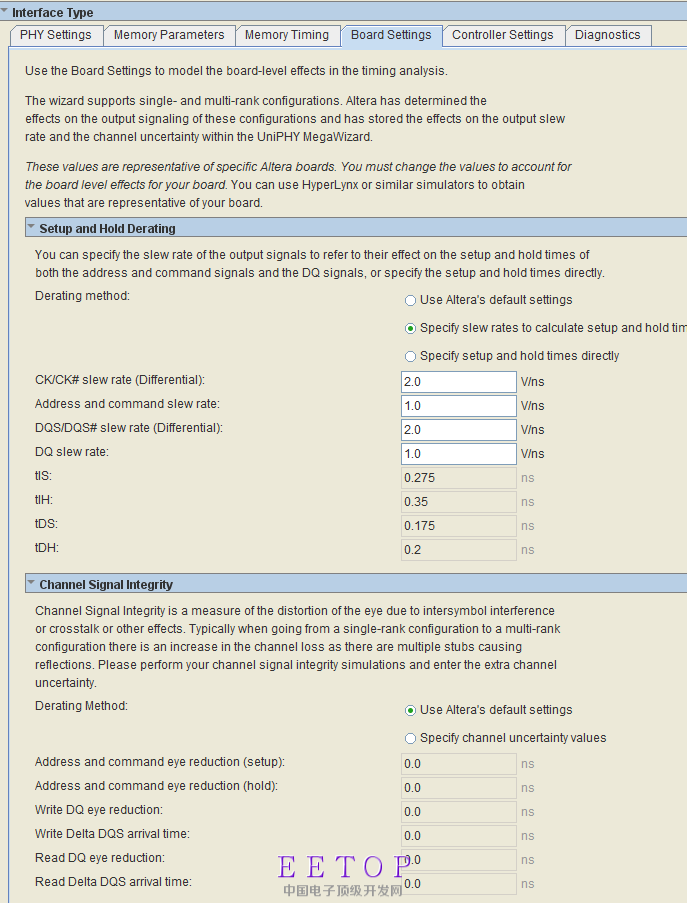

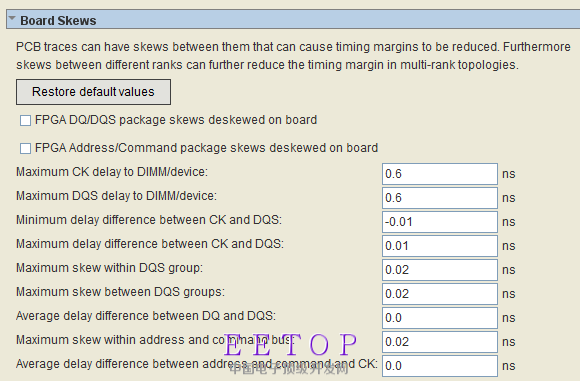

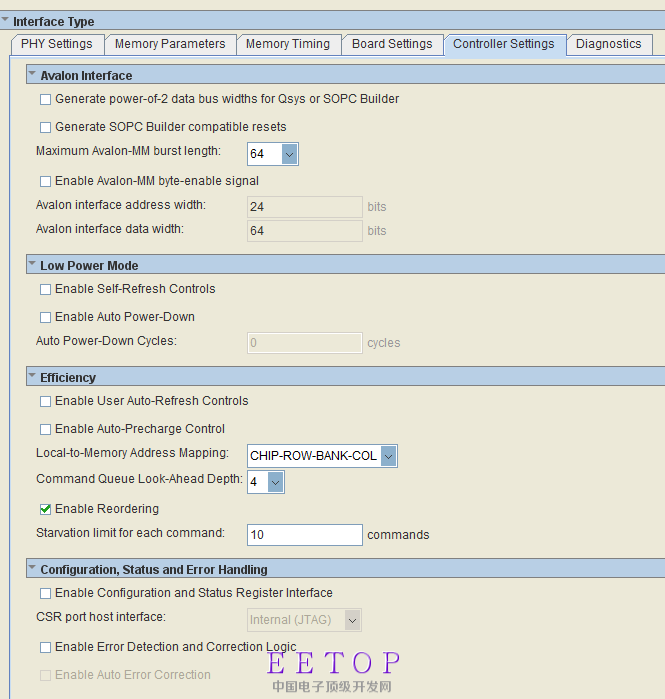

我已经对照datasheet已经设置一遍了,你能帮我看看我大概哪里设置的有问题么

我发现一个问题:对于uniphy来说,oct_rzqin引脚是不是必须要接一个电阻啊?如果不接,悬空是不是会导致初始化失败?如果必须接的话,是要接多大阻值的呢?是不是240ohm

小编这个问题解决了吗。

我和小编遇到了一样的问题。

没解决啊,现在我在不断调整board parameter,没别的办法啊。

仿真都是好好的,所以我觉得应该不是phy和controller设置错的,

你要是发现啥问题也告诉我呗,没准咱俩是一个问题呢

还没有解决,你有什么好的调试方法么,或者你发现是什么问题呢,可以交流一下啊

恩,你用的是开发板还是自己的板子?你用过EMI toolkit了吗,加下qq聊起来方便一点。

我的qq是475615461

虽然没用过Altera,但是感觉你这个rzqin应该是ZQ校准的参考电阻,应该是要接个标准的参考电阻的,阻值是240欧。

查了一下Altera的EMI手册,有这么一句“To calibrate output driver impedance, an external precision resistor, RZQ, connects the ZQ pin and VSSQ. The value of this resistor must be 240-ohm ± 1%."

不知道这个ZQ pin跟你这个rzqin是不是同一个。

我们的电路板是自己做的。实在板上需要有一个240Ohm的电阻吗?

等下加你qq。我的是395871491

是同一个。因为是自己设计的板子,在ddr3的片子有zq的端口,在那里接了一个240ohm的电阻,而在fpga端没有接。感觉应该是对的,这两天我又找了几块成熟设计的板子,也是这么设计硬件的,所以又感到这块是不是没问题

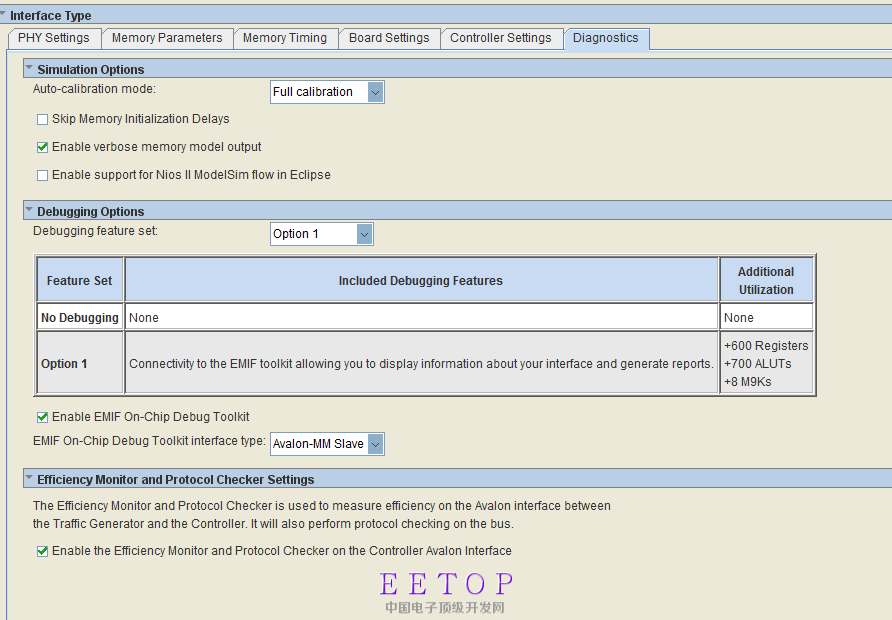

用过toolkit,实际上它只能提供是否校准等结果报告,并不能告诉你具体是什么原因导致初始化失败。按照他的错误提示,我在toolkit的手册上查到的原因是board parameter设置不对,或者是CL、CWL设置不对。

哦,那就不太清楚了,看过一些手册,但没有实际用过

CL CWL Datasheet上应该都有吧。

LZ,我没用过Altera的,但道理应该都是相通的。RZQ是要接一个电阻做参考阻抗用的,阻值是目标阻抗的两倍。如果是高速DDR3(1333以上),这里要接80欧精密电阻,即40欧阻抗,也就是你在IP设置中的RZQ/6的意义。

你说的对,这个地方是应该接一个电阻。另外我初始化失败的原因找到了,一个是引脚分配错了,另外一个是上电之后,复位释放的太快了,在给phy的时钟稳定后再释放复位就没有问题了。还有谢谢上边大家给我的建议,我都有参考,就不一一回复了。

DDR3真的很难吗