抛砖引玉,同步器(一)

小弟,写点关于同步器相对简单的东西,有不对的地方还请各位指点。

说到同步器就得先说亚稳态

在Digital Systems Engineering一书中,亚稳态是这么定义的

When sampling a changing data signal with a clock ... the order of the events determines the outcome.The smaller the time difference between the events, the longer it takes to determine which came first.When two events occur very close together, the decision process can take longer than the time allotted,and a synchronization failure occurs.

亚稳态将导致下一级输入为未知的状态。

为了防止出现亚稳态传输到下一级就要使用同步器了。

在Digital Systems Engineering一书中,同步器是这么定义的

A synchronizer is a device that samples an asynchronous signal and outputs a version of the signal that has transitions synchronized to a local or sample clock.

最常见的就同步器就是两级同步。

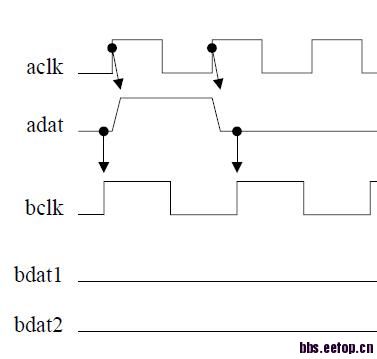

在使用两级同步的时候得注意被采样信号的宽度必须大于采样时钟的周期,不然就会出现下图的问题,漏踩。

换句话说,慢时钟域的信号同步到快时钟域两级同步没问题,快到慢的就可能会出现问题。

今天就先挤这一点,好好整理下思路再上来献丑

非常好,坚持下去,保持更新,好想你的图片没有发布成功,直接点击图片按钮发布,上传完毕后需要点击那个上传的图片,就可以插入到帖子内了。

希望看到小编关于同步器的设计实例

这个版块弄好了,应该会很有意思的!期待啊

你是说rtl代码,还是原理呢?

从信息量的角度来看,快采慢可以,但慢采快应该不行

期待lz的后续内容,刚刚接触到这一块

最近事情比较多,一直没有更新。还往见谅。

初步但算是分成两大类,一部分是控制信号同步,一部分是数据同步。

快到慢,好像可以通过结绳法解决

结绳法(我也把它叫握手法)是解决快到慢脉冲信号的主要方法

10楼的意思应该是:

慢时钟端收到数据要反馈一个信号给快时钟端,快时钟端收到反馈后再接着发下一个数据吧?

也就是说数据的速率其实是比慢时钟要慢的,快时钟每送出一个信号都需要等待慢时钟的反馈吧?

不知道我理解的对不对?

很好的见解~

快时钟域的信号通过展宽方式保证慢时钟域时钟能采样到。

注意数据宽度 保证才一次

很好很好

这个话题,左左右右的博客有很详细的描述,推荐大家看看.

这个话题是很古老的话题,也是永远都有生命力的话题。异步时钟域的处理在低功耗和超大规模逻辑世代越发显得重要。大家有兴趣可以长期关注,并钻研这个技术。

很好很好!

新手,学习了

学习了,这个话题确实是很有意义

两级同步,握手和FIFO

学了FPGA大概一年多了,才入门,学习小编中

想请教一下小编,为何消除亚稳态不用锁存器,而用两级D触发器构成的同步器?(是应为锁存器是电平触发吗?这样会影响电路的稳定性吗?)恳请指教!多谢

两级同步能够消除亚稳态吗? 如果不能百分百消除?一旦出现亚稳态怎么办呢?