关于auroraIP核例化问题

时间:10-02

整理:3721RD

点击:

设计一个4通道的光纤数据采集卡,如果想要把4个通道变成独立通道的话,是用一个aurora核例化4次还是要用4个不同的aurora核?

我记得理化一个ip 选上4个通道接口就可以了

一次例化四个就行

例化一个IP核时,所选的四个通道不是独立工作的,而且必须四个通道都有数据传输才能正常工作。

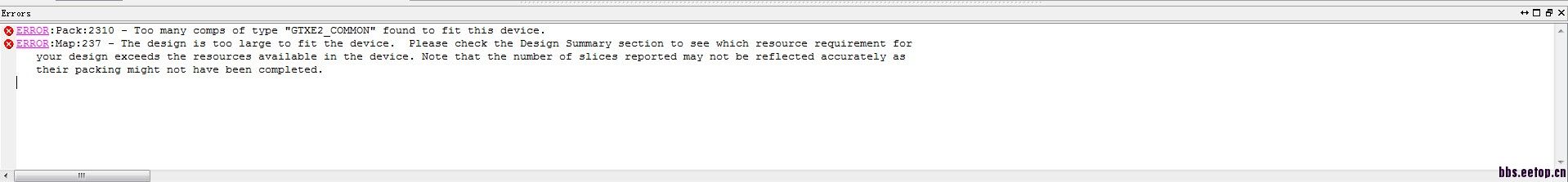

一次例化四个的话布局布线会出错,错误提示如下:

7系列之前,一个GTX有2个收发器;7系列,是4个。

如果4个aurora使用的收发器在一个GTX模块内部,就会出现冲突。这种情况需要将aurora的物理层剥离出来。

好像就是这个问题,我用的是K7芯片,请问将aurora的物理层剥离出来要怎么做呀?

大神帮帮忙解答一下吧,这个问题花了不少时间现在都不知道怎么改了。

aurora的源代码都是公开的,分析一下他的物理层部分,将物理层剥离出来,上面连接4个链路层就好了。

这个。懂了大概的意思,但还是不知道怎么实现。

学习一下,这个看来还有很多可研究的用法啊!

看看最底层收发器的封装部分代码,一个QUAD里的COMMON时钟模块给4个GTP提供时钟。这样你修改源代码,在输出端将COMMON产生的4个给GTP的时钟引出来;其他3个Aurora源代码添加4个时钟输入端,引入底层GTP输入,记得这3个GTP_WRAPPER里的COMMON例化要去掉,因为一个QUAD只有一个COMMON模块,或者你不接参考时钟也行的,就没有必要去掉了。