DDR的预取技术

时间:10-02

整理:3721RD

点击:

各位大侠,我现在使用DDR3,对其预取技术很是不解。

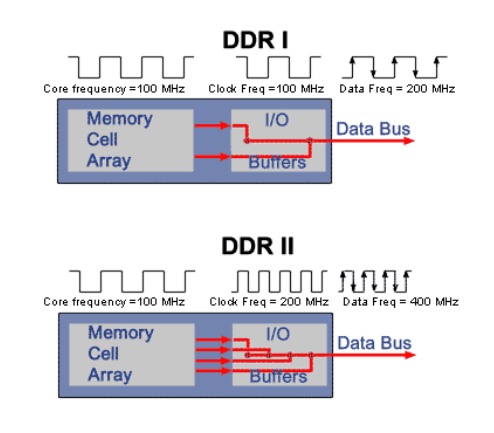

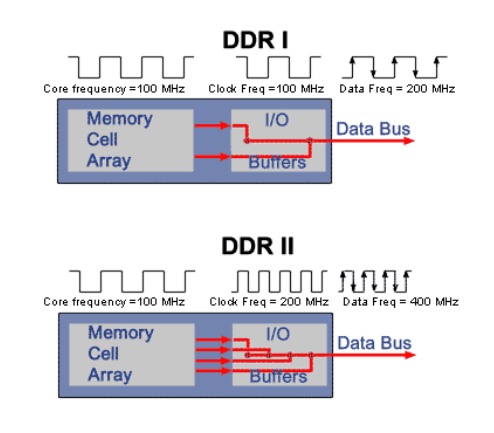

如图,

1.DDR内存工作分为Memory Cell Array,I/O Buffers和Data Bus这三部分是么?如果我的有是64根数据线,也就是位宽为64,这是指这三部分哪部分的位宽呢?图中三部分的位宽分别是多少呢?

2.图中的Memory Cell Array到I/O Buffers的数据传输分别画了2通道和4通道,这2/4通道是指Memory Cell Array的数据由并行的2/4通道传到I/O Buffers中么?

3.DDR说是由于其的预取技术提高了速率,比如说DDR2-400,只需提供核心频率(Memory Cell Array)100MHZ就可以达到数据传输频率(Data Bus)400MHZ。我想问下核心频率不是差分的么?那提供了核心频率,DDR内存工作就不需再提供I/O Buffers和Data Bus的频率了么?

很急,求各位大侠帮忙!感激感激!

如图,

1.DDR内存工作分为Memory Cell Array,I/O Buffers和Data Bus这三部分是么?如果我的有是64根数据线,也就是位宽为64,这是指这三部分哪部分的位宽呢?图中三部分的位宽分别是多少呢?

2.图中的Memory Cell Array到I/O Buffers的数据传输分别画了2通道和4通道,这2/4通道是指Memory Cell Array的数据由并行的2/4通道传到I/O Buffers中么?

3.DDR说是由于其的预取技术提高了速率,比如说DDR2-400,只需提供核心频率(Memory Cell Array)100MHZ就可以达到数据传输频率(Data Bus)400MHZ。我想问下核心频率不是差分的么?那提供了核心频率,DDR内存工作就不需再提供I/O Buffers和Data Bus的频率了么?

很急,求各位大侠帮忙!感激感激!

对于DDR,之前看过一篇文章,不知道理解的对不对,一起探讨下。

问题一:LZ说的64根数据线指的是芯片外部的数据线位宽还是内部Memory Cell Array存储单元的数据位宽?一颗DDR芯片内部存储单元的数据位宽决定了其总线位宽,但是经常在使用时将多片DDR拼在一起扩展总线位宽达到提高访问效率的目的;

问题二:预取技术相当与在DDR内部核心频率下(假设100MHz)一个时钟周期,预取两个存储单元里的数据A[7:0]和B[7:0](假设存储单元位宽8Bit),然后在时钟上升沿发送A,在下降沿发送B,以此达到200MHz的处理速度。对于DDR2则是一个时钟周期预期四次,核心频率不变,外部接口上的时钟速率提高一倍,则DDR2达到400MHz的处理速度;

问题三:DDR芯片总线上的时钟是差分信号双向的与芯片的核心频率是不同的;

大侠有和DDR相关的资料吗?

DDR的核心时钟和接口时钟是两个不同的时钟,他们是有一定的关系的,和预取比有关,以DDR3为例,预取比是8,那么接口时钟频率和核心的时钟频率的比值为4:1。