Nios II 自定义IP 使用问题求助

时间:10-02

整理:3721RD

点击:

我写了一个简单的小代码来实验自定义IP核的读写

开发环境: Quartus 12.0 & Qsys & Nios II 12.0 Software Build Tools for Eclipse

Verilog 代码如下:

module LED_module

(

input CLK,

input nRST,

input read,

input write,

input address,

output [31:0]readdata,

input [31:0]writedata,

input [3:0]byteenable,

input chipselect,

output [3:0]LED_out

);

//Write data

reg [31:0]rLED1;

reg [31:0]Enable;

always @ ( posedge CLK or negedge nRST )

if( !nRST )

begin

rLED1 <= 32'd1;

Enable <= 32'd1;

end

else if( write & chipselect & !address )

begin

if( byteenable[0] ) rLED1[7:0] <= writedata[7:0];

if( byteenable[1] ) rLED1[15:8] <= writedata[15:8];

if( byteenable[2] ) rLED1[23:16] <= writedata[23:16];

if( byteenable[3] ) rLED1[31:24] <= writedata[31:24];

end

else if( write & chipselect & address )

begin

if( byteenable[0] ) Enable[7:0] <= writedata[7:0];

if( byteenable[1] ) Enable[15:8] <= writedata[15:8];

if( byteenable[2] ) Enable[23:16] <= writedata[23:16];

if( byteenable[3] ) Enable[31:24] <= writedata[31:24];

end

//Read data

reg [31:0]rdata;

always @ (*)

if( !nRST ) rdata <= 32'd0;

else if( read & chipselect & !address ) rdata <= rLED1;

else if( read & chipselect & address ) rdata <= Enable;

else rdata <= 32'd0;

assign readdata = rdata;

assign LED_out = Enable[0] ? rLED1[3:0] : 4'd0;

endmodule

软件中自定义结构体

typedef struct {

volatile unsigned long int DATA0;

volatile unsigned long int ENABLE;

}LED_STR;

#define LED ((LED_STR *) LED_MODULE_0_BASE)

软件主程序如下:

int main(void)

{

unsigned long a,b;

a = LED->DATA0;

b = LED->ENABLE;

printf("LED = %ld\n",a);

printf("En = %ld\n",b);

while (1){

LED->DATA0++;

usleep(800000);

LED->ENABLE++;

usleep(800000);

}

return 0;

}

发生的问题就是

rLED1 (寄存器 偏移量为0) 读写都正常 printf为1

Enable(寄存器 偏移量为1) 无法读写 printf为-595508971

为何~

开发环境: Quartus 12.0 & Qsys & Nios II 12.0 Software Build Tools for Eclipse

Verilog 代码如下:

module LED_module

(

input CLK,

input nRST,

input read,

input write,

input address,

output [31:0]readdata,

input [31:0]writedata,

input [3:0]byteenable,

input chipselect,

output [3:0]LED_out

);

//Write data

reg [31:0]rLED1;

reg [31:0]Enable;

always @ ( posedge CLK or negedge nRST )

if( !nRST )

begin

rLED1 <= 32'd1;

Enable <= 32'd1;

end

else if( write & chipselect & !address )

begin

if( byteenable[0] ) rLED1[7:0] <= writedata[7:0];

if( byteenable[1] ) rLED1[15:8] <= writedata[15:8];

if( byteenable[2] ) rLED1[23:16] <= writedata[23:16];

if( byteenable[3] ) rLED1[31:24] <= writedata[31:24];

end

else if( write & chipselect & address )

begin

if( byteenable[0] ) Enable[7:0] <= writedata[7:0];

if( byteenable[1] ) Enable[15:8] <= writedata[15:8];

if( byteenable[2] ) Enable[23:16] <= writedata[23:16];

if( byteenable[3] ) Enable[31:24] <= writedata[31:24];

end

//Read data

reg [31:0]rdata;

always @ (*)

if( !nRST ) rdata <= 32'd0;

else if( read & chipselect & !address ) rdata <= rLED1;

else if( read & chipselect & address ) rdata <= Enable;

else rdata <= 32'd0;

assign readdata = rdata;

assign LED_out = Enable[0] ? rLED1[3:0] : 4'd0;

endmodule

软件中自定义结构体

typedef struct {

volatile unsigned long int DATA0;

volatile unsigned long int ENABLE;

}LED_STR;

#define LED ((LED_STR *) LED_MODULE_0_BASE)

软件主程序如下:

int main(void)

{

unsigned long a,b;

a = LED->DATA0;

b = LED->ENABLE;

printf("LED = %ld\n",a);

printf("En = %ld\n",b);

while (1){

LED->DATA0++;

usleep(800000);

LED->ENABLE++;

usleep(800000);

}

return 0;

}

发生的问题就是

rLED1 (寄存器 偏移量为0) 读写都正常 printf为1

Enable(寄存器 偏移量为1) 无法读写 printf为-595508971

为何~

神奇了!

真的是晕了..

用SOPC Builder 与NIOS II IDE 就能行了....

求高手解答 030

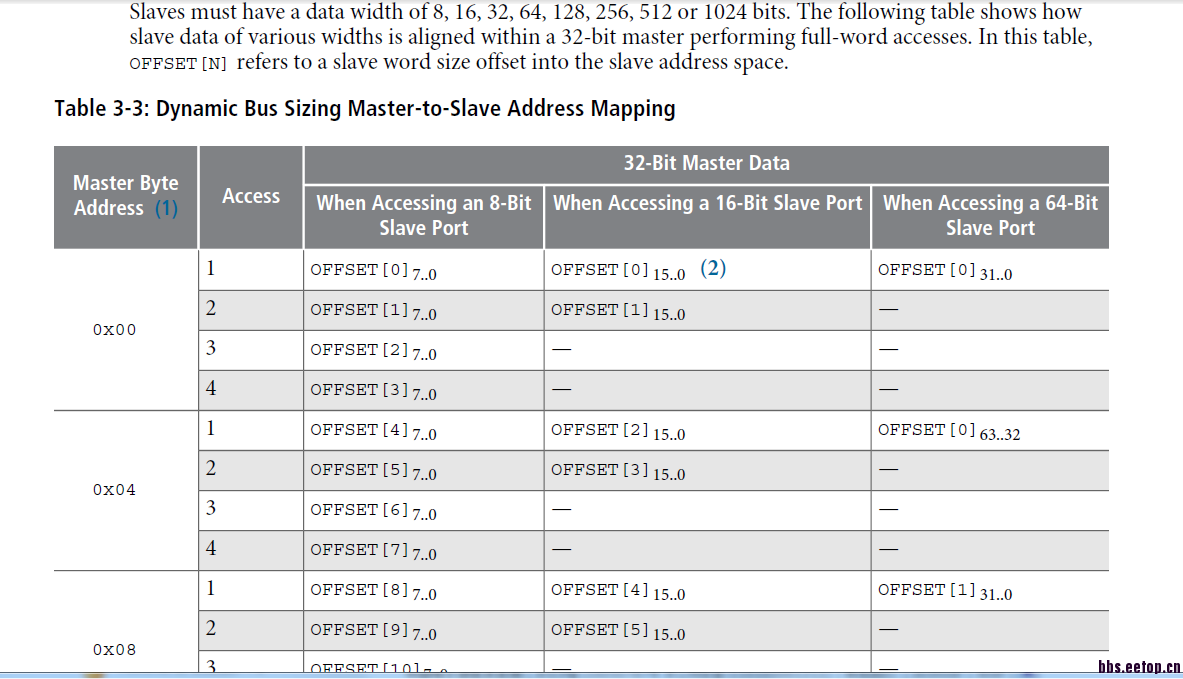

没看出啥问题来,你那个address是地址线的address[2]这个bit吗

address[2]? 不是吧? 其软核内我选择的总线是基于Avalon总线中的Avalon Memory Mapped Interface(Avalon-MM)配置的

地址是选择静态地址对齐

基本上程序应该是没问题

因为用SOPC Builder(Qsys的前身) + NIOS II IDE(Build Tools for Eclipse的前身(?)) 配置后

寄存器皆可正常读取

我在思考是哪些部份在软件改版后需要用户自行设置的部份出了问题

avalon有点忘了,address应该连的address总线的【31:2】,byteenable连接[1:0],一般工具帮你连好的。不行就仿真把,我也没用过qsys。

好的! 我再试试看吧!谢谢您的回复

忘了说我找到资料了

好东西,长经验