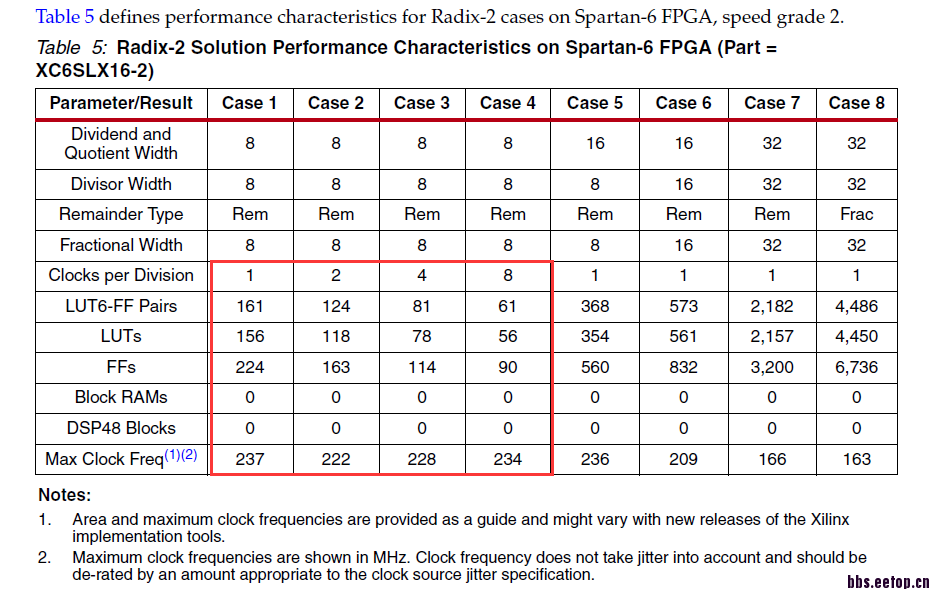

关于xilinx Altera 除法器的比较

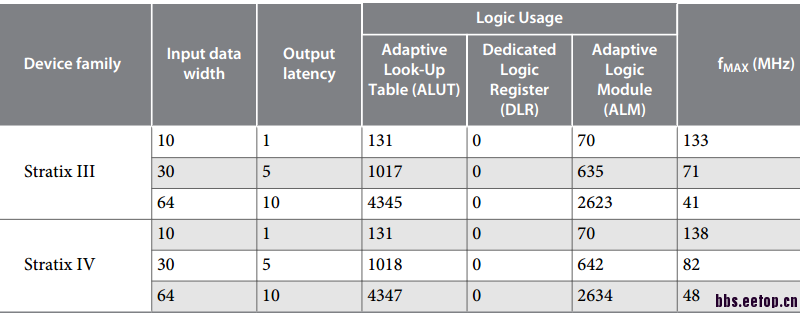

为什么Altera 除法器的 output latency 越大 耗费的资源 反而更多呢? 不是很理解。

xilinx的就是 output latency 大了,就可以省很多资源,只要利用rfd信号 作为输出有效信号 捕捉有效quotient 了!

有没有人懂呢?

那里的latency是每一次除法需要的cycle数,我认为这种情况应该不能pipeline的,这样寄存器及其他一些资源就可以复用。 altera的应该是可以pipeline的,级数越多用到的寄存器就越多。xilinx应该也有这样的IP。

1. Altera除法器的 output latency 大是因为input data width大了,这很合理。 耗费的资源多也是因为位宽,这也很合理。

2. 从小编贴的图上看,Altera的应该不是 pipeline 的。xilinx中1个时钟周期的肯定不是 pipeline 的。只有xilinx的 case 4 有可能是 pipeline 的。

Radix-2 的除法器,每次迭代只能算出一位商值。Radix-2 是除法器中最简单的,它包括恢复余数法、不恢复余数法、Radix-2的SRT算法。第一个最简单。

Altera 可没说是Radix-2的,应该采用了高基数的算法。

Xilinx的,如果用不恢复(non-restoring)算法:

case 4, 运算器只用1个加法器,每clock得到1位商值。省资源,但速度慢。

case 3, 运算器要用2个相同的加法器叠加,每clock得到2位商值。资源多了一点,速度快了一些。

......

亲哪,我觉得你说的比较合理,在哪里看到的啊?有相应的文档吗? 基2 和 高基数 的 各自有哪些优点呢?请教一下

懂了 赞! 是的输入位宽大 latency 大 浪费的资源多!

1. http://bbs.eetop.cn/thread-90133-1-1.html, 台湾某校的。

更详细建议看Israel Koren的《Computer Arithmetic Algorithms》 ,本坛也有。

2. 对于基r, 且r==2**b, 那么每次能算出b位商值。

基2的我在3楼说过。优点是简单。相关资料比较多。

高基数SRT算法,有应用的主要是基4、基8、基16。速度快,但算法复杂,占用资源多。intel后期酷睿2处理器就是用 基16。

更高基数应该用prescaling算法,或其它算法。从xilinx文档上看,比基2高的都用prescaling算法。prescaling算法要用到乘法器。

3. 说altera用高基数算法,是根据你的图猜的。具体哪一种就不知道了。

我好崇拜你啊

正好我知道这个,人各有所长吧?

小编,正在审的帖子就不要发了,内容重复。

?

是说那个 petalinux-config命令出错的帖子吗?

不是的。我上午发的#7楼的帖子,下午2点多还没出现,于是补发了一个(仍然要审核)。发完后发现上午的帖子出现了,于是呼叫小编(审核帖子的人)。