基于Spartan-6 FPGA的DDR2设计经验总结

在基于FPGA的SOPC系统设计中,我们一般都需要外扩内存,而随着存储器工艺的发展,大容量的DDR2内存越来越便宜,在嵌入式领域中也使用的越来越多,Xilinx的Spartan-6 FPGA内嵌了MCB硬核控制器,这极大地方便了我们使用DDR2内存,本文就使用DDR2内存,从原理图设计、PCB设计到EDK环境的使用流程要点作一个说明,欢迎大家来补充说明,如有不当之处也请高手指正。

1.MCB支持DDR2的速率范围为250 Mb/s到800 Mb/s,支持的时钟为125 MHz到400 MHz。

2.Spartan-6 FPGA内部一般都有两个或以上的MCB,如果只用到一个,优先选择使用MCB3。

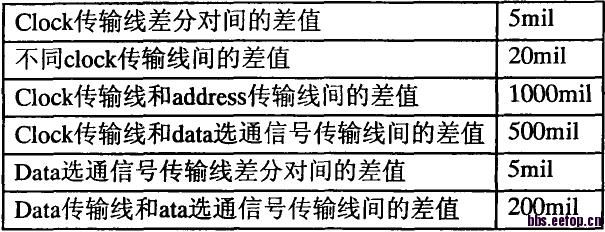

3. DDR2各信号PCB设计时必须进行阻抗匹配,如下是一经验数据可供参考:

4.DDR2使用1.8V的VDD电压,VREF参考电压为0.9V, 一般要求VREF电压为VDD电压的一半,并且能随时反映VDD电压的变化,故可以采用两个一样的电阻串联分压得到VREF电压,典型阻值为20K欧姆,精度为百分之一。

VREF走线参考:

1) 走线宽度:建议20mil以上。

2) 走线间距:建议25mil以上。

3) 包地走线:条件允许下。

4) 去耦电容:尽量靠近IC的管脚处,常用两个数量级电容滤波

(100nF和1nF)。

5. 时钟线差分对之间跨接精度为百分之一的100欧姆电阻,差分端接要靠近DDR2器件端。

6.电路板的阻抗控制在50~60ohm,差分线为100~120ohm。

7.VTT布线要求:

1)走线宽度:最小150mil,一般在表层或底层进行孤岛铺铜。

2)上拉电阻:常用阻排,通常直接放置在VTT铜皮上并就近打孔。

3)去耦电容:每4个电阻(或一个4电阻阻排)放置一个去耦电容,常用0.1uF电容。

4)储能电容:在VTT孤岛铜两端各放置两个电容,常用4.7uF和220uF电容。

8.当数据线地址线负载较重时,VTT 的暂态电流峰值比较大,一般要考虑用专门的电源管理芯片来产生VTT电压,设计时最大电流需要达到3A以上。

9.Spartan-6 FPGA 的MCB硬核需要两个特殊的引脚,RZQ PIN和ZIO PIN。

RZQ PIN是必须的,一定要选择一个和MCB在同一BANK内的引脚。RZQ PIN脚需要通过一个电阻连接到地,电阻阻值为输入阻抗的两倍,如输入阻抗为50欧姆,则RZQ PIN脚需要串接100欧姆的电阻到地。ZIO PIN是可选的,当要用到软件校正功能时才会用到该引脚,ZIO PIN在原理图上不需要有任何连接,悬空就可以了。

10.XILINX提供两个灵活易用的工具软件来使用MCB,一是用在EDK嵌入式开发环境下的MPMC(Multi Port Memory Controller),二是ISE环境下MIG(Memory Interface Generator),MIG主要用在非嵌入式环境下有FPGA逻辑来使用MEMORY的情况,用户只需要编写用户侧的接口逻辑可以了,详细的DDR2控制时序由XILINX的Memory Controller IP核实现,用户不用关心,具体可以参考Spartan-6 FPGA Memory ControllerUG388 (v2.3) 文档,这里不再赘述。EDK环境详细配置步骤我制作了一个视频,大家直接看下就明白了,在EDK环境下可以很容易的建立一个Memory Test工程进行测试.

访问下面网址观看视频:http://v.youku.com/v_show/id_XNDE5NjczOTU2.html

最后提一下,XILINX的SP601开发套件就是使用的DDR2内存,它的设计原理图可以作为一个很好的参考资料,大家可以到XILINX官网去下载原理图和相关资料。

下载地址:http://www.xilinx.com/products/boards-and-kits/EK-S6-SP601-G.htm

好东东!

好东西呀,正好。

markmarkmarkmark

markmarkmarkmark

根本看不清楚。还不如发个文档贴出来

DDR2使用1.8V的VDD电压,VREF参考电压为0.9V, 一般要求VREF电压为VDD电压的一半,并且能随时反映VDD电压的变化,故可以采用两个一样的电阻串联分压得到VREF电压,典型阻值为20K欧姆,精度为百分之一。

这个VREF验证过可以这样直接分压用吗?

稳定和可靠性怎么样?

好东西

GOOD book ON IC DESIGN

围观!

要是更详细就更好了,多谢!

good, up up!

赞赏!111

xie xie xie xie xie xie

感觉 DDR3 更容易些///

好东西~

这个关键看电流,一般分压式设计满足需求

这个本没有什么特别的。

SP601是DDR2

S6-IVK是 DDR3

参考着没什么问题。比较容易。

看着太累了

好东西呀,正好。

好东东啊

好东西呀,正好。

感謝! 很好的使用心得分享!

09年已经搞过DDR!

09年在S6的工程样片上搞了一下,很不顺利!

确实不错,值得收藏。

kankan

非常感谢

感觉 DDR3 更容易些///

very good

视频不是很清晰,看不到上面的字