spartan 6里的锁相环的使用

时间:10-02

整理:3721RD

点击:

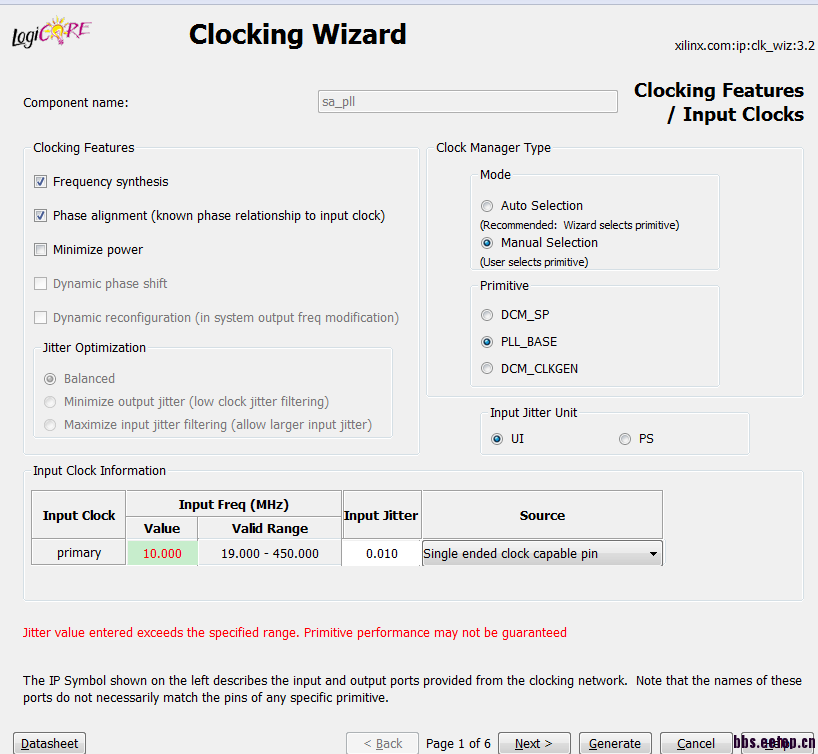

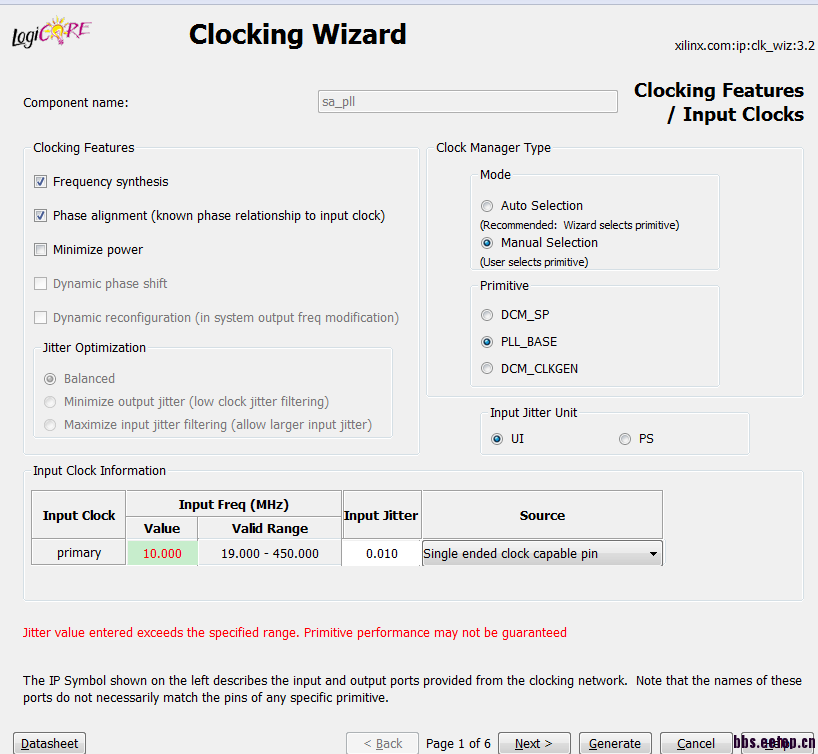

我想用pll把10MHz的输入倍频到100MHz, 这个100MHz很多地方要用到 我希望它的时钟质量很好,所以想使pll ,而不是dcm.

但是pll 输入频率范围貌似有限制,必须大于19MHz, 怎么破? 莫非要先用DCM 提高几倍频率 然后再使用pll 吗?

ds162 看看dcm的频率限制

ds162 看看dcm的频率限制