xilix DDR3 IP 求助

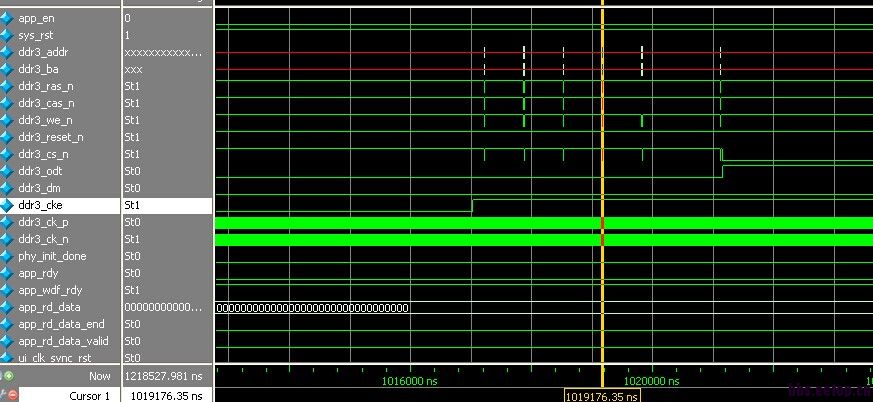

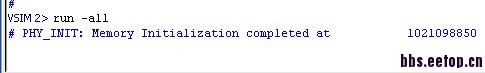

modelsim命令框中截图:[attach]590876[/attach]显示初始化完成的时候,phy_init_done就应该拉高电平啊 为啥一直是低电平尼?

初始化时候的局部仿真放大截图:

我没有开发板,我只是生成IP,然后添加例化IP,只做仿真验证,在modelsim命令框中截图:显示初始化已经完成的时候,为啥phy_init_done 信号没有拉高?没拉高就说明没有初始化完成,就不能进行下一步的读写操作啊,麻烦大虾们给指点一下,多谢咯

modelsim命令框中截图

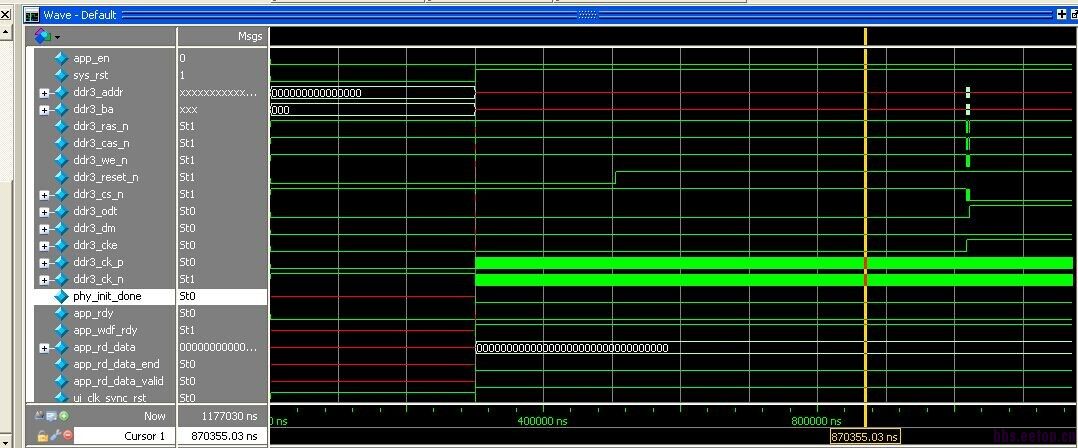

上面的两个图片,第一个是仿真全部截图: 第二个是modelsim命令框中截图:补上去,不好意思

最好的办法,把你的tb贴上来

可以先仿真MIG自带的测试仿真文件,然后对照MIG的tb,应该可以找到问题。

module tb_ddr3_ctrl;

// Inputs

reg sys_clk_p;

reg sys_clk_n;

reg clk_ref_p;

reg clk_ref_n;

reg app_wdf_wren;

reg [31:0] app_wdf_data;

reg [3:0] app_wdf_mask;

reg app_wdf_end;

reg [28:0] app_addr;

reg [2:0] app_cmd;

reg app_en;

reg sys_rst;

// Outputs

wire [14:0] ddr3_addr;

wire [2:0] ddr3_ba;

wire ddr3_ras_n;

wire ddr3_cas_n;

wire ddr3_we_n;

wire ddr3_reset_n;

wire [0:0] ddr3_cs_n;

wire [0:0] ddr3_odt;

wire [0:0] ddr3_cke;

wire [0:0] ddr3_dm;

wire [0:0] ddr3_ck_p;

wire [0:0] ddr3_ck_n;

wire app_rdy;

wire app_wdf_rdy;

wire [31:0] app_rd_data;

wire app_rd_data_end;

wire app_rd_data_valid;

wire ui_clk_sync_rst;

wire ui_clk;

wire phy_init_done;

// Bidirs

wire [7:0] ddr3_dq;

wire [0:0] ddr3_dqs_p;

wire [0:0] ddr3_dqs_n;

// Instantiate the Unit Under Test (UUT)

ddr3_ctrl uut (

.sys_clk_p(sys_clk_p),

.sys_clk_n(sys_clk_n),

.clk_ref_p(clk_ref_p),

.clk_ref_n(clk_ref_n),

.ddr3_dq(ddr3_dq),

.ddr3_addr(ddr3_addr),

.ddr3_ba(ddr3_ba),

.ddr3_ras_n(ddr3_ras_n),

.ddr3_cas_n(ddr3_cas_n),

.ddr3_we_n(ddr3_we_n),

.ddr3_reset_n(ddr3_reset_n),

.ddr3_cs_n(ddr3_cs_n),

.ddr3_odt(ddr3_odt),

.ddr3_cke(ddr3_cke),

.ddr3_dm(ddr3_dm),

.ddr3_dqs_p(ddr3_dqs_p),

.ddr3_dqs_n(ddr3_dqs_n),

.ddr3_ck_p(ddr3_ck_p),

.ddr3_ck_n(ddr3_ck_n),

.app_wdf_wren(app_wdf_wren),

.app_wdf_data(app_wdf_data),

.app_wdf_mask(app_wdf_mask),

.app_wdf_end(app_wdf_end),

.app_addr(app_addr),

.app_cmd(app_cmd),

.app_en(app_en),

.app_rdy(app_rdy),

.app_wdf_rdy(app_wdf_rdy),

.app_rd_data(app_rd_data),

.app_rd_data_end(app_rd_data_end),

.app_rd_data_valid(app_rd_data_valid),

.ui_clk_sync_rst(ui_clk_sync_rst),

.ui_clk(ui_clk),

.phy_init_done(phy_init_done),

.sys_rst(sys_rst)

);

initial begin

// Initialize Inputs

sys_clk_p = 0;

sys_clk_n = 0;

clk_ref_p = 0;

clk_ref_n = 0;

app_wdf_wren = 0;

app_wdf_data = 0;

app_wdf_mask = 0;

app_wdf_end = 0;

app_addr = 0;

app_cmd = 0;

app_en = 0;

sys_rst = 0;

//sys_rst = 0;

#300000

sys_rst = 1'b1;

#660000

sys_rst = 1'b1;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

reg sys_clk;

reg clk_ref;

initial begin

sys_clk = 1'b0;

clk_ref = 1'b1;

end

// Generate system clock = twice rate of CLK

always

sys_clk = #1.25 ~sys_clk;

// Generate IDELAYCTRL reference clock (200MHz)

always

clk_ref = #2.5 ~clk_ref;

always @(*)

begin

sys_clk_p = sys_clk;

sys_clk_n = ~sys_clk;

end

always @(*)

begin

clk_ref_p = clk_ref;

clk_ref_n = ~clk_ref;

end

endmodule

这就是我的TB文件

你的tb没有ddr的仿真模块

有FPGA开发和验证相关的 岗位。 如有兴趣请发简历到blisy@tom.com

有DDR3 模块

// Instantiate the Unit Under Test (UUT) ddr3_ctrl uut ( ), 这个就是, ddr3_ctrl 是顶层,ddr3 ip例化在顶层里面的

ddr3_ctrl是你的控制逻辑吧,你的tb中缺少ddr3的仿真模型(ddr3_simulation_model)

ddr3_ctrl里面只有我例化的ddr3 ip 读写操作没有,也没有任何控制逻辑啊,说白了只有一个IP core,我只仿真,只给复位信号,看看其他信号的变化,就这么简单。

你这样仿真不行,必须要有ddr3的仿真模型才可以。

你最好参考一下ip中生成的tb,学习一下再用

楼上说的对,你必须要添加仿真模型,否则你的IP后端没有东西不是,也就是你的初始化过程永远完成不了,请参照example_design里面的sim文件夹里的文件,ddr3_model.v以及wiredly.v,然后看它的tb是怎么写的,另外为了加快初始化进度,可以修改SIM_BYPASS_INIT_CAL变量,这样初始化会快一些

小编方便的话,可以留个方式交流下

学习学习

我的QQ:751880266

没有ddr3的仿真模型,而且还有个参数要拉出来SIMULATION = “true”;

使用example_design的话,初始化结束后会用它自带的traffic_generator模块生成后续的读写命令;自己修改的话,初始化结束后就按自己想要的来

MIG生成的控制器是怎么初始化DDR2的呢?就是那个phy_init_done信号是如何生成的?用modelsim仿真DDR2模型时,读写数据和读写地址都是由ISE自动生成的,我仿真的DDR2,是8次读8次写,现在我想自己设定读写地址和读写数据和读写次数,但是连phy_init_done信号都不拉高。向您请教~

DDR2没有研究过,不过理论上,用户不应该修改初始化代码,等初始化结束后才能自己控制读写吧

并没有修改初始化代码,ISE可以生产DDR2控制器和DDR2模型以及仿真文件(读写地址和读写数据的产生),目前想通过app_*信号自己给输入,可是phy_init_done信号一直不拉高,即DDR2初始化不成功,用户无法进行读写数据和地址的输入。但是同样的模型和控制器,在ISE自己生成的测试文件下就能正确初始化和读写。phy_init_done信号是如何产生的?需要用户给什么输入信号吗?已经纠结好长时间了

你自己写的测试文件,仿真时加DDR2的模型了没?自己写的话就是把顶层中的traffic_generator模块替换掉,其它的不应该变,仿真的话仍然要采用它那个model文件

先用example跑。不要改任何东西。开始初始化时间挺长,100ms吧

请问答主是否方便留个qq,我正在做关于DDR读写的项目,看了很多资料还是不太清楚,能否详细咨询下你?ps:主要问题是,现有两个数据获取和ddr测试的工程,试图合并成一个工程实现获取的数据写入ddr中。

呃,不是太明白你的需求。如果是和DDR3协议相关的问题,我还能回答一下,如果是MIG核之类的,我其实用的也不多……

我手头上只有ddr。不过应该可以从ddr3反推回去。主要的疑问是我不知道要实现将fpga片上block ram 的数据存到ddr中,需要怎么操作?我的理解是用mig生成一个ddr control 然后将fpga上的数据输出与ddr中的数据输入相连。这是硬件层次的,那么软件层次的话,因为是嵌入式开发,有用到microblaze软核,是否需要在sdk中编写程序之类。由于不太清楚此流程导致走了很多弯路,到现在思路都很分散。

软件我不怎么懂,microblaze也没用过。硬件实现的话,我感觉你可以例化一个MIG,然后自己改写traffic_gen部分,也就是从BRAM读出数据,然后写入DRAM?

请问改写traffic_gen,是删掉top文件里的traffic_gen部分,自己写代码控制app_信号,还是修改traffic_gen里面的文件,这个traffic_gen看不懂啊

自己写,把它替换掉即可。你可以找找MIG的手册,看看到底怎么用。