请教一下异步Reset和时钟同步的问题

我想提这么个问题:我的设计里有个SPI Slave模块,用的是Master过来的SPICLK。

那该模块里的异步reset是不是应该和SPICLK同步一下?

但问题是,Master并不总是提供SPICLK,有可能要到它想和你通信时才发时钟,通信完了就停止。

那这个SPI模块不就有可能reset不了?

想请教下这种情况下,reset该怎样同步比较好?

解决办法:

1):后面的逻辑全部用ASYNC reset.在上电的时候,没有clock也可以复位成功。

2):做一个clock mux。刚上电的时候使用一个稳定的clock,然后切换到spi_clk

把异步复位信号同步到时钟上,依然是异步复位,不用时钟也可以复位。

设计中说的异步复位的同步 指异步复位信号释放的时候与时钟同步。

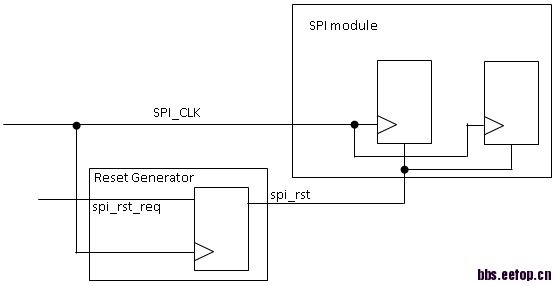

再贴个同步电路图吧:

这个帖子里有。

http://bbs.eetop.cn/viewthread.php?tid=370203&rpid=7352291&ordertype=0&page=1#pid7352291

去学习了下,收获不少,支持!

最好不要用时钟切换,那样属于门控时钟,不太好。

可以使用一个外部时钟,PLL出来一个2陪于SPICLK的时钟SYSCLK,用SYSCLK来当你的控制时钟,SPI口的SPICLK,数据和复位都要经过SYSCLK的同步,其中数据和复位的同步要用同步后的SPICLK当CLKEN。然后同步后的复位就可以当做异步复位来使用了

muylor你说的方法,在RST释放的时候,整个电路是满足了Recovery/Removal,可是在RST有效的时候,rst_sync直接由RST异步控制产出,相当于前两级的D触发器没有起到作用。

2)的方法不太好吧……时钟的平稳切换肯定也需要spi_clk参与的吧?而且感觉这样SPI模块的时钟域就更复杂了……

thank you!

恕我无知,想追问2个问题:

1)rst_sync为什么要用2级FF同步?又没有牵扯到异步过度,1级不行吗?

2)这样RST解除后,需要2个CLK才能解除rst_sync。但有的SPI Master是有几个数据想通信就给几个clock,一个都不会多给,那rst_sync要等到master给clock时才解除,而且要消耗2个clock,通信结果不就会出错了吗?

rst_sync为什么要用2级FF同步?又没有牵扯到异步过度,1级不行吗?

Ans: It is used to avoid meta-stable problem, which happens to design which has no fixed relationship between the input signal (reset in this example) and clock.

1. 用两级同步是因为: 这个两个寄存器的复位时异步释放的(复位信号和时钟完全异步),这两个寄存器的Recovery/Removal不能保证。

所以可能产生亚稳态。如果只有一个寄存器,那么在复位释放时,D端输入是1,复位状态下寄存器是0,这样就有一个跳变,那么这个跳变可能引起亚稳态,所以要用两个寄存器。第二个寄存器在复位释放时不会产生亚稳态是因为它的输入是0,状态也是0.

2. 你这里是异步复位,只要上电复位就可以了,以后每次访问都不会再复位了。当然在复位释放后需要至少两个clock cycle来确保释放完成。

希望我讲明白了,如果没讲明白,你先记下吧,这个是异步复位同步化的标准电路,以后慢慢悟吧。

上面的回复应该能说明这个问题。

谢谢你的回答,完全明白了!

对于2),其实我的项目里不是只有上电时才reset的,我们的SPI把软件复位做成了异步的,

把软件复位送到reset模块里要生成异步复位信号,才有了这样的难处。

谢谢你的建议!

这种设计我见过的,就是SPI的PAD进来后都直接用系统clock打2拍,然后SPI_CLK当成控制信号而不是时钟来用,这样整个SPI模块就是系统时钟域的了,就好做了。

可惜我们的SPI不是这样设计的。

谢谢回答!

我也知道一般打2拍是为了防止亚稳态,只是没想明白这样的情况为什么会有亚稳态。

看了10楼的解释已经明白了。

你的这种时钟完全由外部供给,没有自己系统时钟的情况,是无法做同步reset的

所以处理办法就是只用异步的reset(如果现在纠结的问题就是reset如何处理的话)

你的spi_slave模块直接的reset用CS信号就好了吧 你只要保证用的时候master的时序关系 这里其实是不会有亚稳态的问题的

学习一下!