例化DDR2控制器,利用DCM产生差分时钟出现的问题

时间:10-02

整理:3721RD

点击:

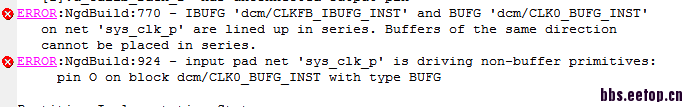

在顶层模块中例化DDR2控制器(利用MIG产生),所需的差分时钟信号sys_clk_p和sys_clk_n由DCM产生,报错如图,有没有做过的指导一下?差分时钟由DCM生成可以吗?

不对吧,这个不是从时钟芯片输入的ref clk么?怎么是由DCM产生的呢?而且DCM印象中不能产生差分信号吧。

那DDR2控制器所需的差分信号怎么生成?需要两对,sys_clk_p、sys_clk_n和clk200_p和clk200_n。还有,DCM生成的clk0和相移180组成的是差分时钟信号吗?

1,差分时钟只能外部供给,不能用dcm等产生,一个时钟和一个180°相移的时钟组合不等于一个差分时钟,差分信号是有电气特性要求的。

2,可以只用一对差分时钟,即sys_clk_p和sys_clk_n,在选择refclk时钟源时选择use_system_clk,就不必用clk200_p和clk200_n。

3,也可以不用差分时钟,在生成ip核时,选择system clock源的时候选择来自bufg,那么你就可以用dcm生成一个时钟接到ddr ip核就可以了

哦哦,谢谢,已经在仿真文件中直接给差分输入了。请问你做过DDR2控制器吗?把用MIG生成的控制器例化成子模块调用时会出现各种各样的问题,时钟解决了,可phy_init_done信号一直是unknown状态。 。

两个全局buffer串联了,找到指出来的那个“BUFG”,改成“BUF”,就可以用了

最近同样在搞ddr,在论坛上看见不少你的帖子,能否留个QQ交流下