抛砖引玉,同步器(二)

时间:10-02

整理:3721RD

点击:

最近小弟所在公司已经n久没发工资,所以也就闲了。慢慢把自己这几年弄过的东西总结下,发上来。

先从最简单的开始。

在(一)里面说了快采慢的事,这里继续说下慢采快容易出现的问题,和简单的解决方法。

先从最简单的开始。

在(一)里面说了快采慢的事,这里继续说下慢采快容易出现的问题,和简单的解决方法。

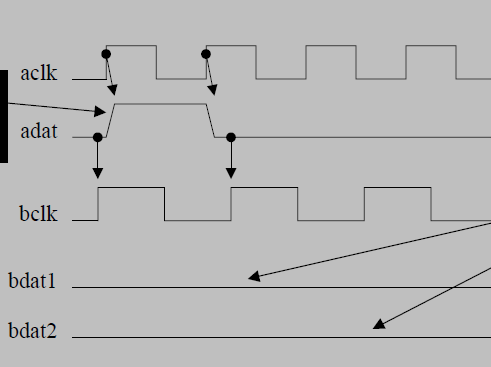

快时钟域信号到慢时钟域有可能的情况是:

快时钟域信号宽度比慢时钟信号周期窄,导致漏采。

解决的方法有:

1.

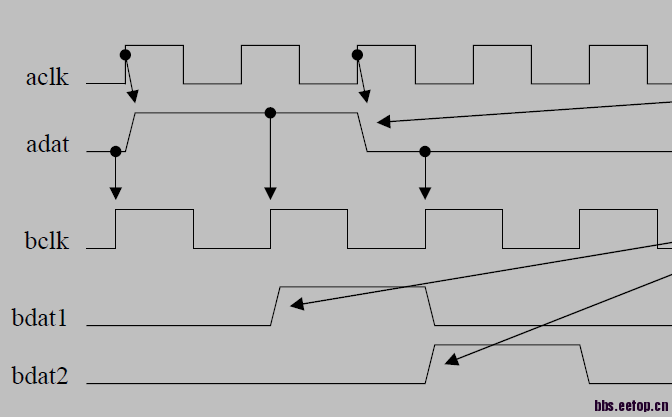

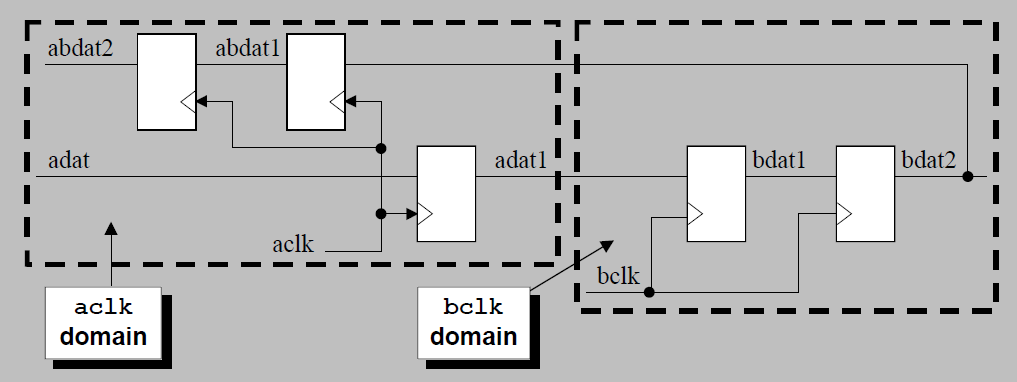

将快时钟域信号延长,至少有慢时钟周期的一到两个周期宽

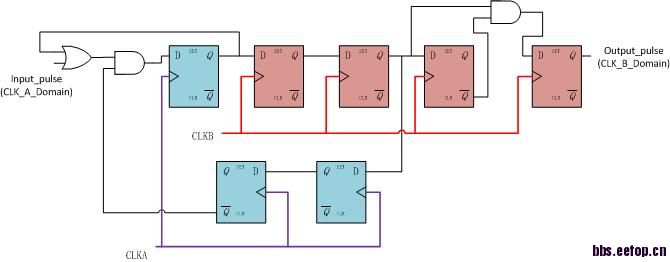

2. 使用反馈的方法,快时钟域信号有效直到慢时钟域有反馈信号,表示已经正确采样此信号,然后快时钟域信号无效。

通过反馈的方式很安全,但是从上图可以看出来延时是非常大的。慢时钟采快时钟信号,然后反馈信号再由快时钟采。

以上是简单的单个信号同步器的基本方法。

第二种方法没怎么理解怎么实现,小编能解释的详细一点吗

第二种方法简单说,假设高为有效,a_clk时钟域的信号一直拉高,然后在b_clk时钟域中采,采到稳定的高后,这个信号被反馈回a_clk,在a_clk时钟域中由两级同步采后,作为a_clk时钟域里拉低信号的使能。

给力啊,顶起

好文,应顶一下

支持一下小编

长见识了!

谢谢啊

谢谢小编的总结!

学习了

很棒!

很不错的基础知识,赞