求教:将一个reg型数据assign给wire,为什么wire的1在仿真中变成了x?

时间:10-02

整理:3721RD

点击:

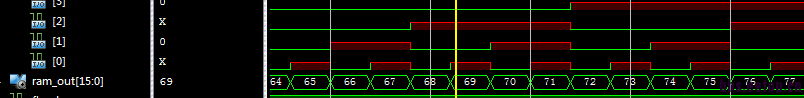

各位大侠,如图所示,下面的是上面的是16位wire,下面的是16位reg,把reg的值用assign赋给wire。

图中上面的的【0】 【1】 【2】等等是把16位信号展开。

reg中的值是+1递增的,那么wire也是,看最低位【0】信号中,0是正确的,但是该位为1的时候,为什么就显示为X呢?请问有人遇到过这个问题吗?

不胜感激。

自顶一下。

把相关代码贴出来看看,很有可能哪里写错了!

非常感谢!

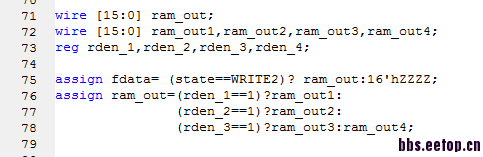

这是程序,ram_out是从ram_out1-4里面四选一,仿真波形里面这个ram_out都是没有错的,然后再将ram_out赋值给fdata,fdata前面的那个判断条件也是满足的。

检查fdata,总觉得还有别的信号在驱动它。

同意acgoal,fdata是否是输出,在其它模块有赋值为1?