十万火急,modelsim SDRAM功能仿真,见鬼了...

时间:10-02

整理:3721RD

点击:

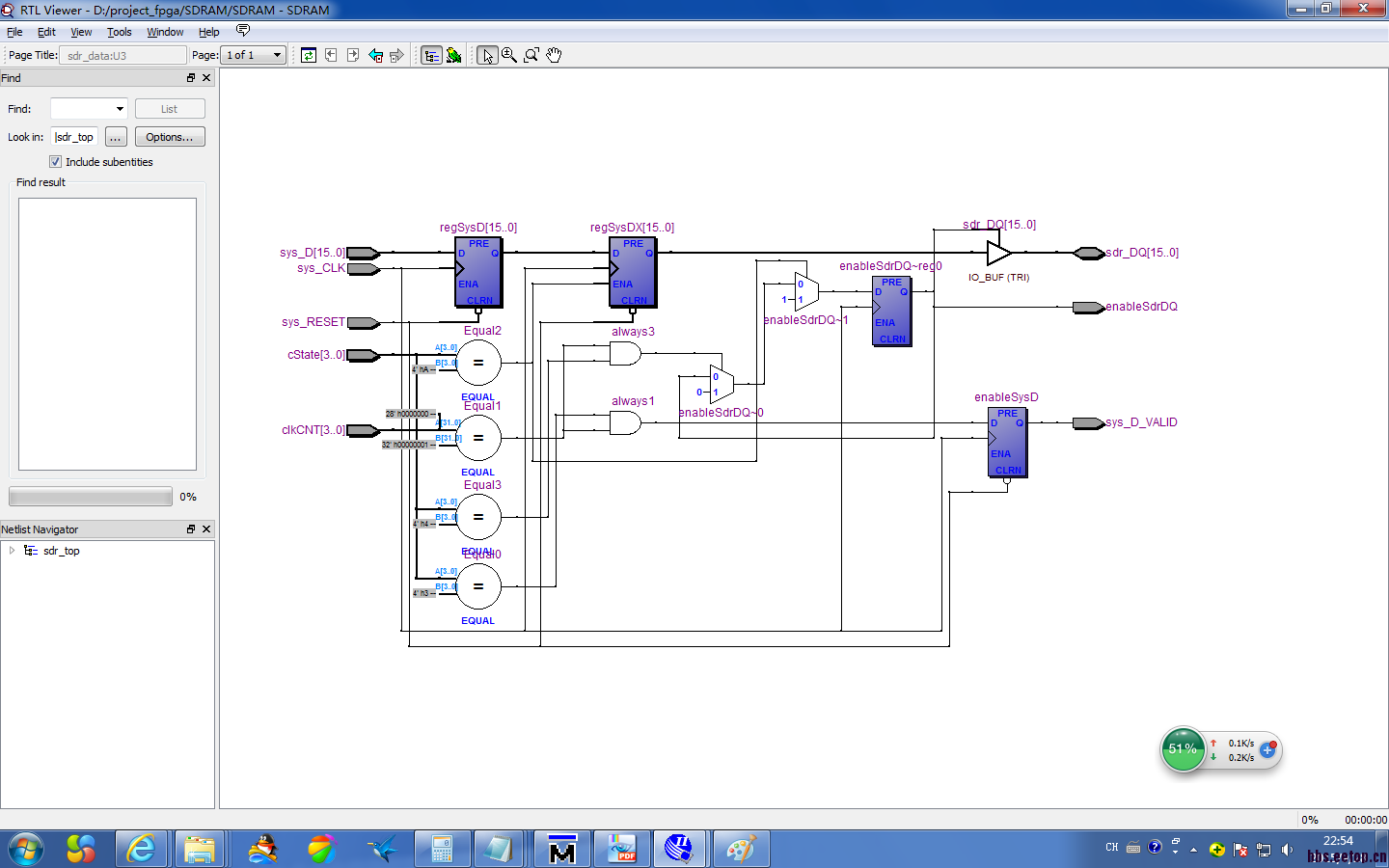

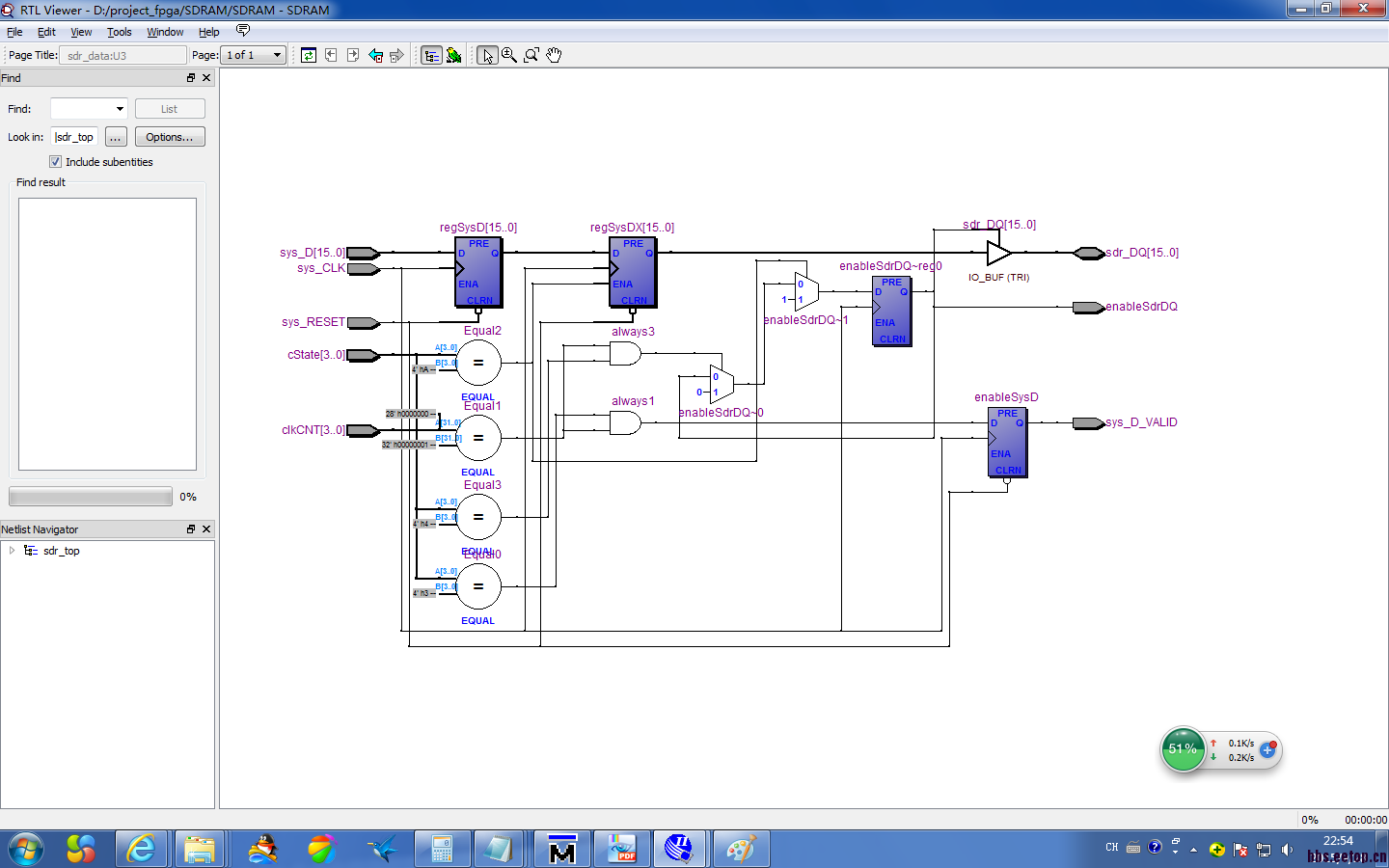

SDRAM Verilog写操作功能仿真,想必大家都熟悉吧,在module data.v中如下。

困惑就是sdr_DQ在仿真中总是16'bxxxx_xxxx_xxxx_xxxx。即使单一使用备注assign #tDLY sdr_DQ[15:0] =4'hABCD;也无法完成赋值。

已确认在top.v模块中有链接,在data.v/top.v中都有设置sdr_DQ是inout型。同时enableSdrDQ与regSysDX[15:0]都有值,就是sdr_DQ始终为xxxx

data.v中的部分代码:

module sdr_data(

sys_CLK,

sys_RESET,

sys_D, // data bus

sys_D_VALID, // data valid

cState,

clkCNT,

sdr_DQ,

enableSdrDQ, // sdr data

);

**********

inout [15:0] sdr_DQ;

**********

assign #tDLY sdr_DQ[15:0] = (enableSdrDQ==1'b1) ? regSysDX[15:0] : 16'bzzzz_zzzz_zzzz_zzzz;

//assign #tDLY sdr_DQ[15:0] =4'hABCD;

always @(posedge sys_CLK or negedge sys_RESET)

if (!sys_RESET)

regSysDX <= #tDLY 16'h0000;

else if (cState == c_WRITEA)

regSysDX <= #tDLY regSysD[15:0];

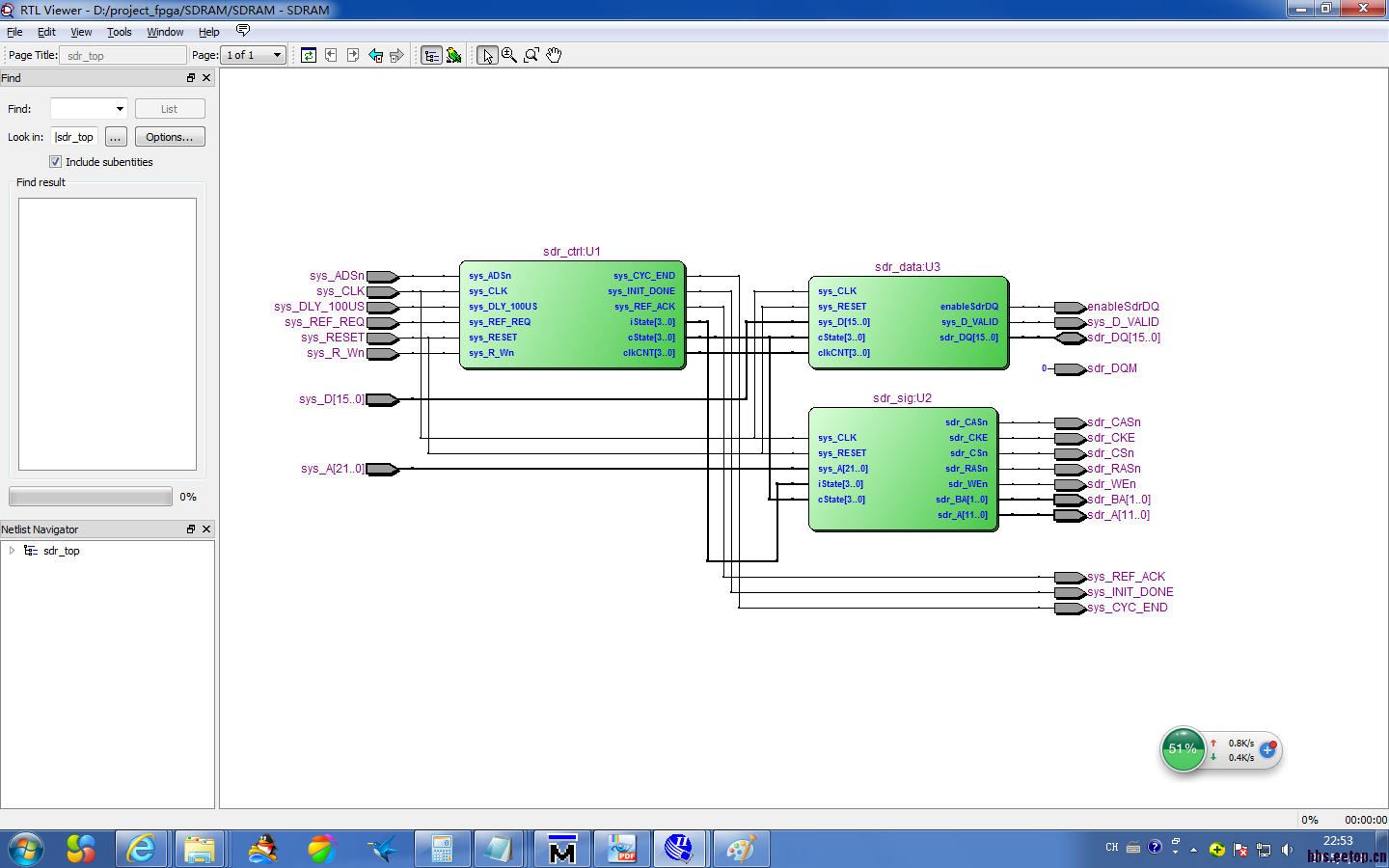

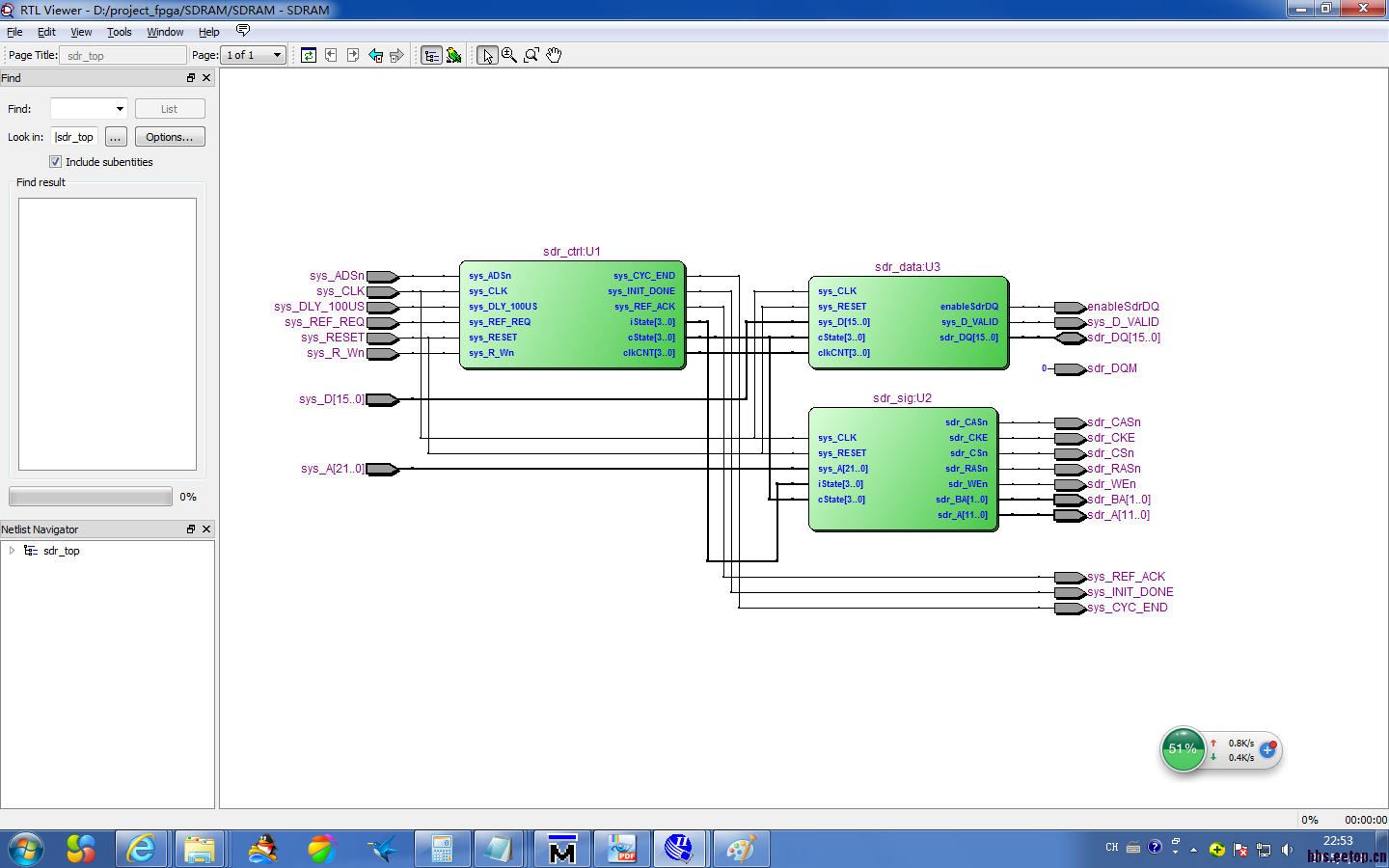

top.v中端口声明都有链接,quarters2 RTL viewer图片如下:

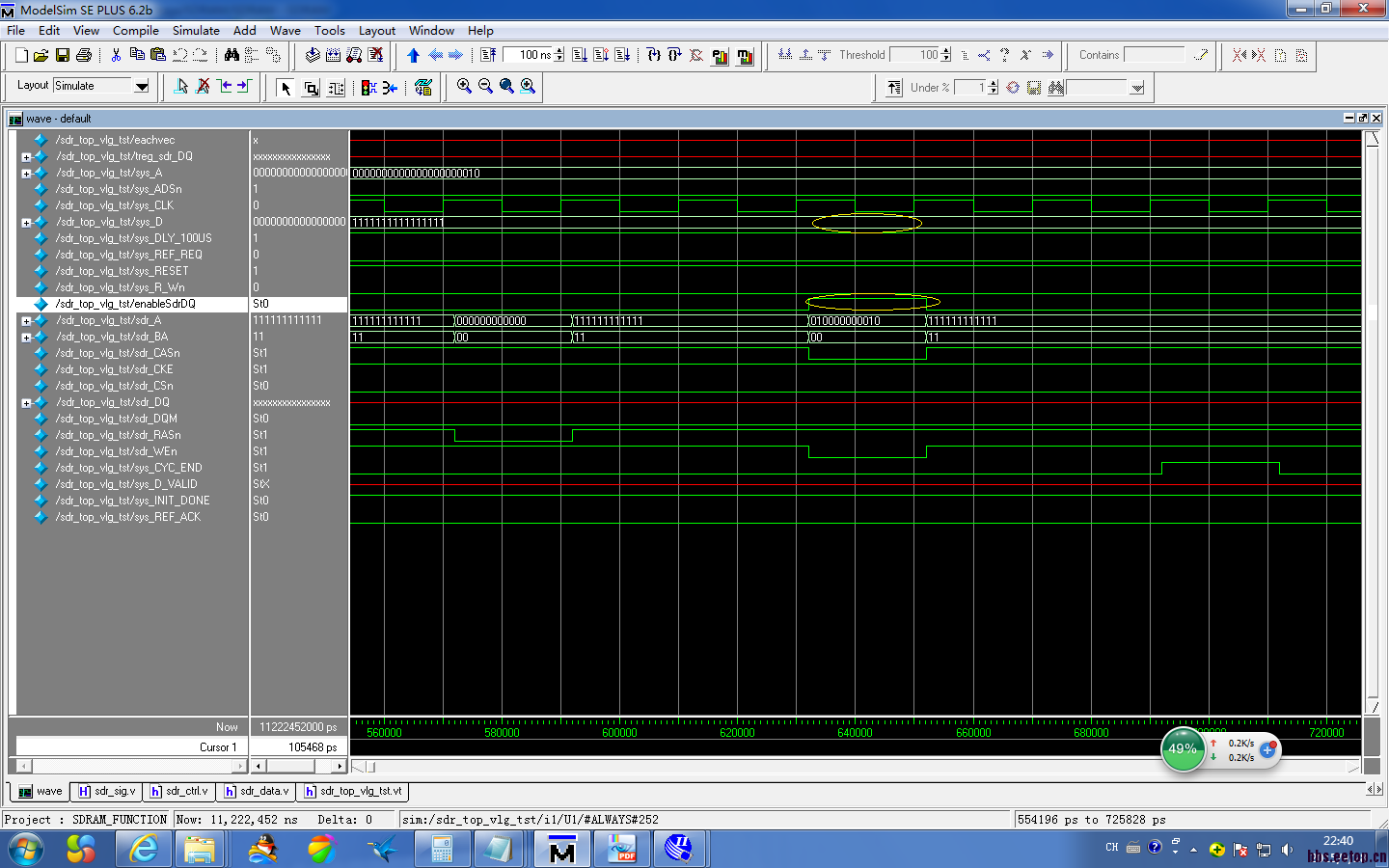

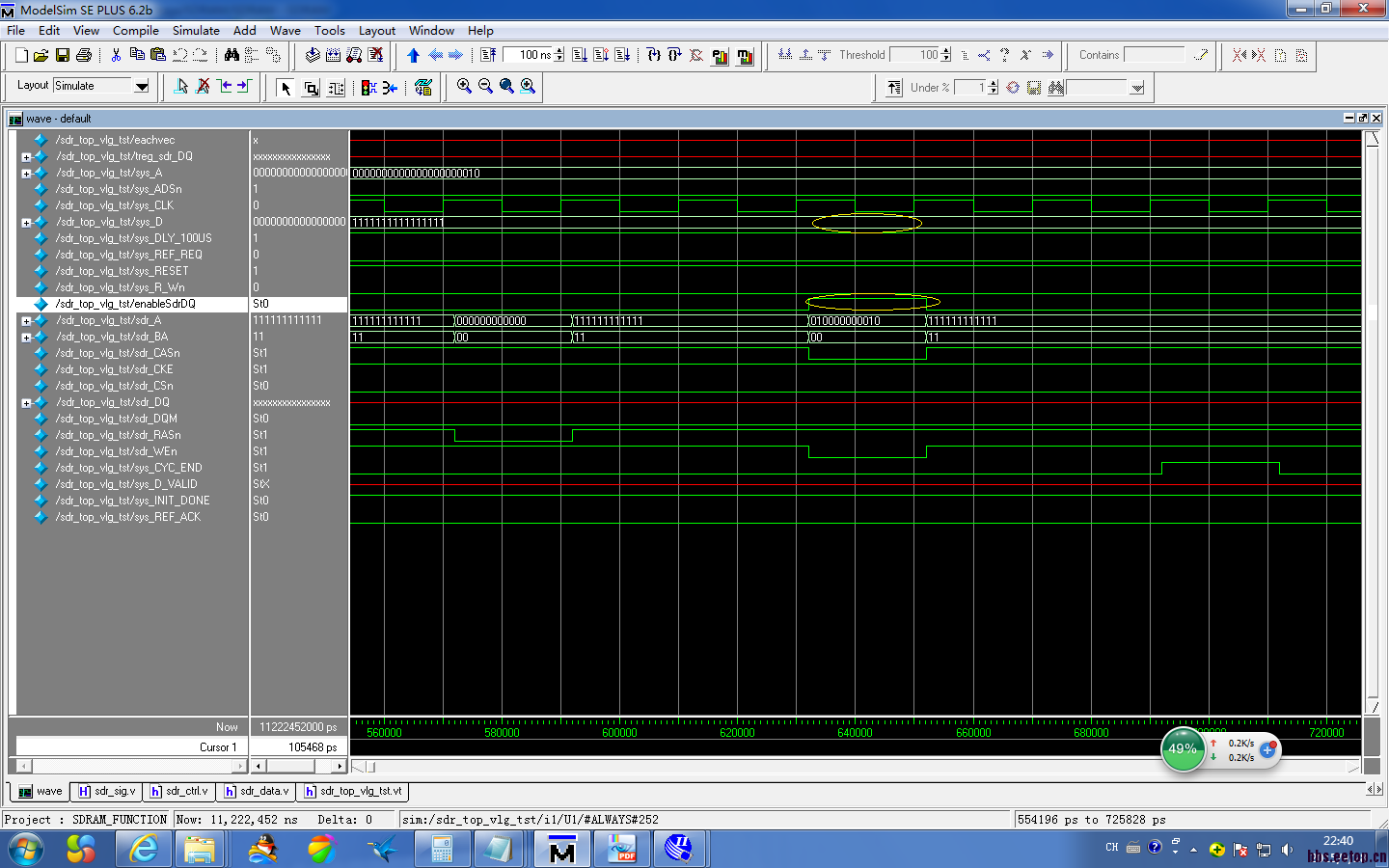

仿真图:可以看到sdr_dq始终为xxxx,真是捉急啊,即使用assign连续赋值都没用,这到底是哪里不对?

困惑就是sdr_DQ在仿真中总是16'bxxxx_xxxx_xxxx_xxxx。即使单一使用备注assign #tDLY sdr_DQ[15:0] =4'hABCD;也无法完成赋值。

已确认在top.v模块中有链接,在data.v/top.v中都有设置sdr_DQ是inout型。同时enableSdrDQ与regSysDX[15:0]都有值,就是sdr_DQ始终为xxxx

data.v中的部分代码:

module sdr_data(

sys_CLK,

sys_RESET,

sys_D, // data bus

sys_D_VALID, // data valid

cState,

clkCNT,

sdr_DQ,

enableSdrDQ, // sdr data

);

**********

inout [15:0] sdr_DQ;

**********

assign #tDLY sdr_DQ[15:0] = (enableSdrDQ==1'b1) ? regSysDX[15:0] : 16'bzzzz_zzzz_zzzz_zzzz;

//assign #tDLY sdr_DQ[15:0] =4'hABCD;

always @(posedge sys_CLK or negedge sys_RESET)

if (!sys_RESET)

regSysDX <= #tDLY 16'h0000;

else if (cState == c_WRITEA)

regSysDX <= #tDLY regSysD[15:0];

top.v中端口声明都有链接,quarters2 RTL viewer图片如下:

仿真图:可以看到sdr_dq始终为xxxx,真是捉急啊,即使用assign连续赋值都没用,这到底是哪里不对?