异步电路上FPGA 付费求助

时间:10-02

整理:3721RD

点击:

有高手吗?解决异步电路上FPGA的问题,求兼职,付费。

什么问题

简单描述一下是什么问题,不然谁知道会不会呢

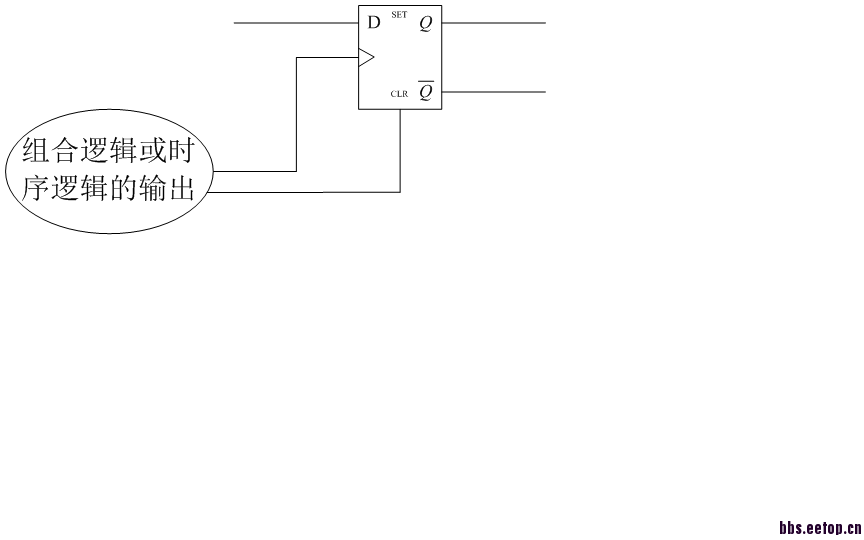

电路中包含大量使用图片所示的寄存器:其时钟和复位直接使用由其他组合逻辑或者时序逻辑产生的信号。全电路的寄存器总数约为1000多个,使用图片连接方式的寄存器有上百个,无法一一对其进行约束。FPGA综合产生了较大的困难。

求助ing

将组合逻辑的时钟信号当成选择信号,再另外使用一个标准时钟即可。如

always @(posedge X)

Q <= D;

改为

always @(posedge CLK)

if (X)

Q <= D;

复位的做法也类似。

如果X的上升脉冲大于CLK的周期,则要另外用edge detector电路来产生选择信号。

抱歉,是大于2个周期时。若小于1个周期则须提高时钟频率。

5楼是个好方法

首先FPGA中的时钟资源有限,有些FPGA可能只有2级时钟网络,也就是说每个网络上的时钟是由同一条金属线驱动的,每个寄存器都可以连接到这条金属线上,这样做的目的就是为了同步。

其次,不太理解你这样设计的目的是什么?感觉到基本的数字设计都不清楚。是为了低功耗还是为了错开时钟上升沿的瞬时功耗?如果是前者最好是像5楼那样来做。如果是后者,希望将时钟分频后在进行处理,这样就不会如此了,另外,你的复位信号一定需要用时钟打两拍,避免异步设计的亚稳态。

你是ASIC的代码移植到FPGA?

若是FPGA时钟资源允许的话,5楼是正解

付费?

谢过小编了