fsl总线数据收发问题

时间:10-02

整理:3721RD

点击:

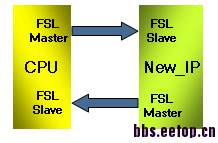

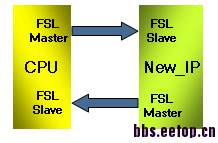

大家好,当前有一个项目需要把采集的数据发送出来,考虑采用microblaze + fsl自定义IP的方式实现。

cup中fsl master的fifo统一设置为16,测试中发现,当cup中fsl slave的fifo设置为较小时,数据传输没有问题,当fifo设置较大时,程序一直停在write_into_fsl()这个指令(512及以下成功,4096失败)。该指令由xilinx提供,用于实现寄存器到fsl输出总线的传输,这是一个阻塞型的指令,处理器将一直停留在该指令直到fsl fifo的full flag变低。根据手册,这个问题应该是由发送fifo full引起的,但是问题是都还没有写他为什么fifo会变满呢?xps下cup中的fsl master和slave均使用bus_rst对其进行的复位。自定义IP设计为接收8个数据后,发送一定量的数据(较大)。请问大家遇到过这样的问题吗?求解? for (i=0; i<8; i++) { write_into_fsl(input_0, input_slot_id); } for (i=0; i<FSL_RX_BUFFERSIZE; i++) { read_from_fsl(output_0, output_slot_id); }

cup中fsl master的fifo统一设置为16,测试中发现,当cup中fsl slave的fifo设置为较小时,数据传输没有问题,当fifo设置较大时,程序一直停在write_into_fsl()这个指令(512及以下成功,4096失败)。该指令由xilinx提供,用于实现寄存器到fsl输出总线的传输,这是一个阻塞型的指令,处理器将一直停留在该指令直到fsl fifo的full flag变低。根据手册,这个问题应该是由发送fifo full引起的,但是问题是都还没有写他为什么fifo会变满呢?xps下cup中的fsl master和slave均使用bus_rst对其进行的复位。自定义IP设计为接收8个数据后,发送一定量的数据(较大)。请问大家遇到过这样的问题吗?求解? for (i=0; i<8; i++) { write_into_fsl(input_0, input_slot_id); } for (i=0; i<FSL_RX_BUFFERSIZE; i++) { read_from_fsl(output_0, output_slot_id); }

你是如何修改fifo深度的?是直接修改的代码,还是通过交互界面设置?fifo有支持的最大深度,看看你配置的深度是不是超过了最大深度?