使用ADV7125芯片控制的VGA显示问题

时间:10-02

整理:3721RD

点击:

小弟最近在做VGA实验,采用的时钟是59.944MHz,使用DCM进行了一次1.5倍分频,显示为800x600@60,随便写了一个代码,让显示屏全部显示白色,但是显示器没反应,我觉得自己是不是把原理理解错了,所以把代码贴在这里,希望各位不吝赐教。

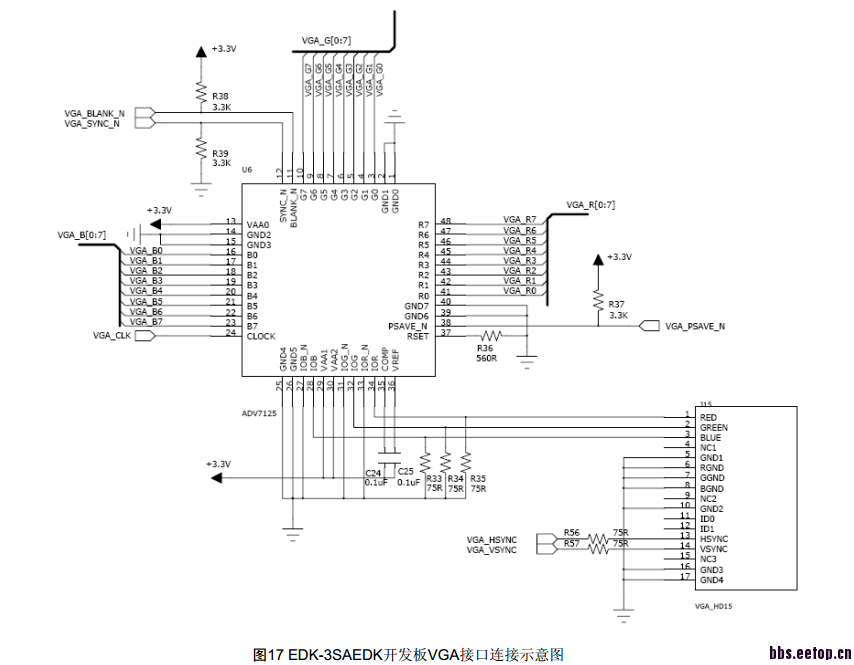

另外附上了一张图板子用户手册上ADV7125和VGA连接的示意图。

- //////////////////////////////////////////////////////////////////////////////////

- module vga_dis(

- clk,rst_n,

- hs,vs,

- vga_r,vga_g,vga_b,

- );

- input clk; //59.944MHz

- input rst_n; //低电平复位

- output hs; //行同步信号

- output vs; //场同步信号

- output [7:0]vga_r; //RGB各8位800X600@60

- output [7:0]vga_g;

- output [7:0]vga_b;

- //-----------

- wire clk_40M;

- DCM1 instance_name (

- .CLKIN_IN(clk),

- .CLKDV_OUT(clk_40M)

- );

- //----------vs,vh产生----------

- reg[10:0] x_cnt; //行坐标

- reg[10:0] y_cnt; //列坐标

- always @ (posedge clk_40M or negedge rst_n)

- if(!rst_n) x_cnt <= 11'd0;

- else if(x_cnt == 11'd1056) x_cnt <= 11'd0;

- else x_cnt <= x_cnt+1'b1;

- always @ (posedge clk_40M or negedge rst_n)

- if(!rst_n) y_cnt <= 11'd0;

- else if(y_cnt == 11'd628) y_cnt <= 11'd0;

- else if(x_cnt == 11'd1056) y_cnt <= y_cnt+1'b1;

- reg valid;

- always @ (posedge clk_40M or negedge rst_n)

- if(!rst_n) valid<= 1'b0;

- else if((x_cnt>11'd216)&&(x_cnt< 11'd1017)&&(y_cnt> 11'd27)&&(y_cnt<11'd627))

- valid <= 1'b1;

- else valid <= 1'b0;

- assign vs=(x_cnt<= 11'd4 )?1'b0: 1'b1;

- assign hs= (y_cnt<= 11'd128 )? 1'b0 : 1'b1;

- reg [23:0]vga;

- always @ (posedge clk_40M )

- if(!valid) vga <= 24'd0;

- else

- vga<=24'b1111_1111_1111_1111_1111_1111;

- assign vga_r = vga[23:16];

- assign vga_g = vga[15:8];

- assign vga_b = vga[7:0];

- endmodule

行时序128+88+800+40=1056

帧时序4+23+600+1=628

:dizzy: