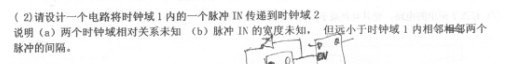

看到以前的一个笔试题,没有思路,求讨论

时间:10-02

整理:3721RD

点击:

脉冲IN宽度未知,居然还比时钟1的周期短,我觉得题我都没看懂

顶!

先拓宽,后采,再变。

1.将clock1中的脉冲遇到跳变后就翻转,生成一个大电平信号

2.用clock2去两拍和三拍采样1的电平

3.在clock2中用上述生成的两个电平信号异或

说得好,谢谢

懂得思路了,谢谢~

但是第一步用verilog怎么实现

题目的意思是两次脉冲间隔的时间足够长,你不用担心前后两次脉冲间的影响。

不是说比时钟1的周期短

到底怎么解决啊?脉冲宽度比时钟域1的周期窄,展宽怎么实现?

你好,讲的很精辟,大概思路懂了,但是有点疑问: 因为两个始终与的相对关系未知,如果两个脉冲间隔小于时钟域2的周期,那么拓宽后的电平就可能采不到,这种情况怎么解决?谢谢!

你很有思考,这个就可以当做设计规格问题,需要按场景。可以淹没,也可以2个宽度变成很长的,只要不淹没。看你项目要求。

这个是我们公司经常出的啊,网上摘抄的面试题

将脉冲信号变成电平信号,用D触发器来实现

解答转载:http://www.cnblogs.com/qiweiwang/archive/2011/09/15/2177562.html

http://www.cnblogs.com/qiweiwang/archive/2011/09/15/2177562.html